4.菜鸟初入FPGA之运算符/缩减运算

0赞 先来说一下关系运算符:

关系运算符有以下四种:

( 1) a<b a 小于 b

( 2) a>b a 大于 b

( 3) a<=b a 小于或者等于 b

( 4) a>=b a 大于或者等于 b

在进行关系运算时,如果申明的关系是假的( false) ,则返回值是 0,如果申明的关系是真的( true) ,则返回值是 1,如果某个操作数的值不定,则关系是模糊的,返回值是不定值。

所有的关系运算符都有着相同的优先级别。关系运算符的优先级别低于算数运算符的优先级别。

详细请查看夏老师的Verilog语法书,这里不做描述

缩减运算符是单目运算符,也有与或非运算。其与或非运算规则类似于位运算符的与或非运算规则,但其运算过程不同。位运算是对操作数的相应位进行与或非运算,操作数是几位数则运算结果也是几位数。而缩减运算则不同, 缩减运算是对单个操作数进行与或非递推运算,最后的运算结果是一位的二进制数。夏老师的书里是这样说的:缩减运算的具体运算过程是这样的:第一步先将操作数的第一位与第二位进行与或非运算,第二步将运算结果与第三位进行与或非运算,依次类推,直到最后一位。

例如:

reg[3:0]B; reg C; C=&B; //等价于: //C=((B[0]&B[1])&B[2])&B[3];

下面看一下例程:

module suojian(rst_n,clk,c); input clk; input rst_n; output reg c; reg [3:0]b;// always @(posedge clk or negedge rst_n) if(!rst_n)begin c <= 0; b <= 4'b1111; end else c <= & b; endmodule

tb文件:

`timescale 1ns/1ns `define clk_period 20 module suojian_tb; reg clk; reg rst_n; wire c; initial clk = 1; always #(`clk_period/2)clk = ~clk; initial begin clk = 0; rst_n = 0; #(`clk_period*5) rst_n = 1; end suojian suojian(.rst_n(rst_n),.clk(clk),.c(c)); endmodule

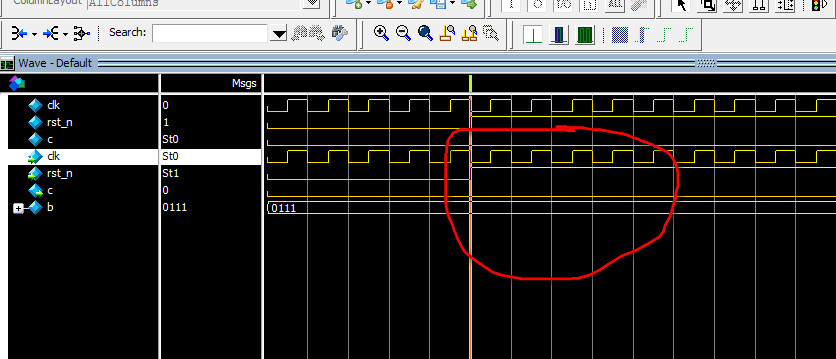

波形:

通过波形我们可以看到,当rst_n=1时,由于b的四个位全部为1 ,:逻辑与"运算后,C的值在下一个时钟沿上升的时候输出C值为高电平

我们更改一下代码,把B的值改为B= 4'b0111后再看一下波形图

可以看到,变量b中有0,逻辑与后 C值一直为0

备注:

Augus仿真的时候大意了,结果出现一个很简单的错误:

** Error: (vsim-3037) E:/Yuzhe_fpga_prj/Blog_pro/suojianyunsuan/suojian_tb.v(21): Missing instance name in instantiation of 'suojian'.

原因是没有例化名,写程序时一定要注意这种小错误,每次编译仿真一次时间都很长,虽然这个程序时间很短,但是要是大工程少了一个例化名而出错,是不是很遗憾

suojian suojian(.rst_n(rst_n),.clk(clk),.c(c));

由于本人能力有限,出错之处的请各位给予帮助.谢谢!

更多资料参考

发烧友小梅哥专版 http://bbs.elecfans.com/zhuti_fpga_1.html

梦翼师兄的炼狱传奇