6.菜鸟初入FPGA之Case语句验证4-16译码器

0赞

发表于 2016/3/26 上午11:09:06

阅读(7633)

本次笔记记录的是4-16译码器的验证

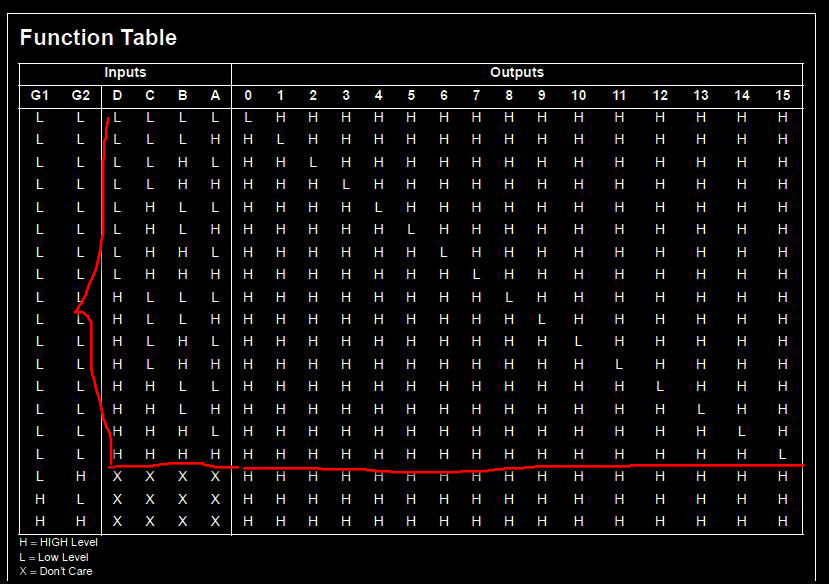

下面我们看一下4-16译码器的真值表

从真值表中我们可以观察到,从十六组数据中取出要写程序的所需要的信息

例程:

module my_4_16(a,b,c,d,out);

input a;

input b;

input c;

input d;

output reg [15:0]out;

always @(a,b,c,d) begin//a,b,c,d作为敏感信号

case({a,b,c,d})

4'b0000 : out = 16'b0000_0000_0000_0001;

4'b0001 : out = 16'b0000_0000_0000_0010;

4'b0010 : out = 16'b0000_0000_0000_0100;

4'b0011 : out = 16'b0000_0000_0000_1000;

4'b0100 : out = 16'b0000_0000_0001_0000;

4'b0101 : out = 16'b0000_0000_0010_0000;

4'b0110 : out = 16'b0000_0000_0100_0000;

4'b0111 : out = 16'b0000_0000_1000_0000;

4'b1000 : out = 16'b0000_0001_0000_0000;

4'b1001 : out = 16'b0000_0010_0000_0000;

4'b1010 : out = 16'b0000_0100_0000_0000;

4'b1011 : out = 16'b0000_1000_0000_0000;

4'b1100 : out = 16'b0001_0000_0000_0000;

4'b1101 : out = 16'b0010_0000_0000_0000;

4'b1110 : out = 16'b0100_0000_0000_0000;

4'b1111 : out = 16'b1111_1111_1111_1111;

//由于刚好16组数据,所以default语句不需要在写

endcase

end

endmodule

///`tb

`timescale 1ns/1ns

module my_4_16_tb;

reg a;

reg b;

reg c;

reg d;

wire [15:0] out;

my_4_16 my_4_16(

.a(a),

.b(b),

.c(c),

.d(d),

.out(out)

);

initial begin

a=0; b=0;c=0;d=0;

#100;

a=0; b=0;c=0;d=1;

#100;

a=0; b=0;c=1;d=0;

#100;

a=0; b=0;c=1;d=1;

#100;

a=0; b=1;c=0;d=0;

#100;

a=0; b=1;c=0;d=1;

#100;

a=0; b=1;c=1;d=0;

#100;

a=0; b=1;c=1;d=1;

#100;

a=1; b=0;c=0;d=0;

#100;

a=1; b=0;c=0;d=1;

#100;

a=1; b=0;c=1;d=0;

#100;

a=1; b=0;c=1;d=1;

#100;

a=1; b=1;c=0;d=0;

#100;

a=1; b=1;c=0;d=1;

#100;

a=1; b=1;c=1;d=0;

#100;

a=1; b=1;c=1;d=1;

#200;

$stop;

end

endmodule 仿真波形图:

本次程序读懂真值表后不难写出,因为全部二进制书写,比较浪费时间.同样的,3-8译码器更容易写出

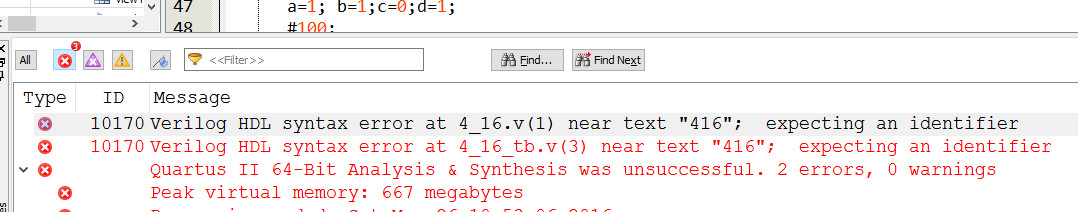

注: 程序模块名命名时不要以纯数字命名例如"4_16",编译时会报错

更多资料参考

发烧友小梅哥专版 http://bbs.elecfans.com/zhuti_fpga_1.html

梦翼师兄的炼狱传奇