11.菜鸟初入FPGA之异步复位同步释放

0赞

发表于 2016/4/6 下午5:11:54

阅读(7830)

针对数字系统的设计,我们经常会遇到复位电路的设计,对初学者来说不知道同步复位与异步复位的区别与联系,本次笔记对这个问题简要的阐述下.

同步复位原理:同步复位只有在时钟沿到来时复位信号才起作用,则复位信号持续的时间应该超过一个时钟周期才能保证系统复位。

异步复位原理:异步复位只要有复位信号系统马上复位

两种方式各有优缺点

下面我们分别看下两种方式的区别

1.同步复位

always @ (posedge clk )//or negedge rst_n if (!rst_n) b<= 1'b0; else b <= a;

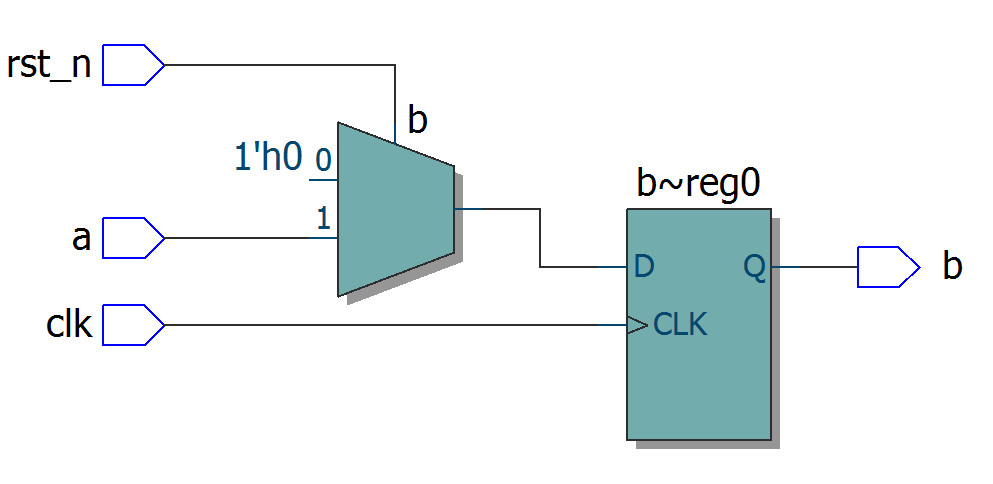

RTL:

2.异步复位

always @ (posedge clk or negedge rst_n )// if (!rst_n) b<= 1'b0; else b <= a;

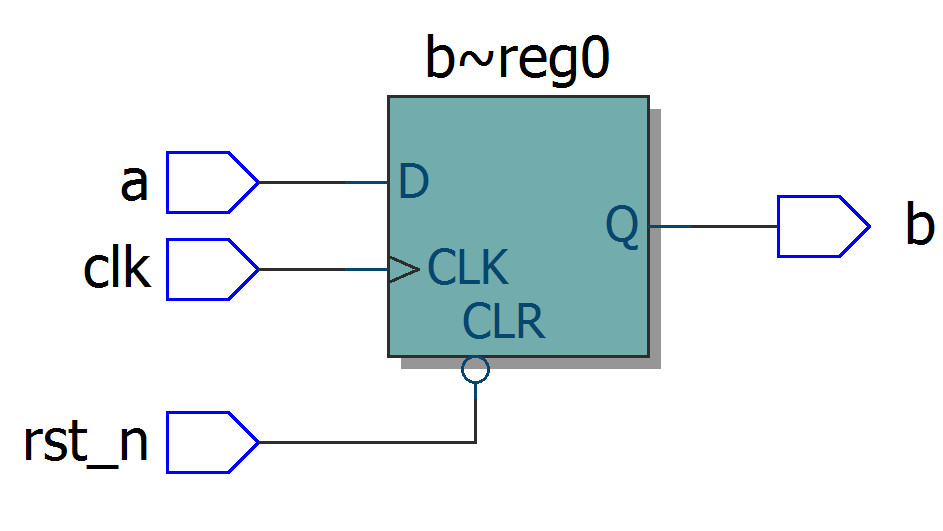

RTL:

和异步复位相比,同步复位没有用上寄存器的CLR端口,综合出来的实际电路只是把复位信号rst_n作为了输入逻辑的使能信号。那么,这样的同步复位势必会额外增加FPGA内部的资源消耗。

同步复位的好在于它只在时钟信号clk的上升沿触发进行系统是否复位的判断,这降低了亚稳态出现的概率;它的不好上面也说了,在于它需要消耗更多的器件资源,这是我们不希望看到的。

那么我们可以想到能不能把两者结合起来,这样,既解决了同步复位的资源消耗问题,也解决了异步复位的亚稳态问题。

3. 异步复位、同步释放

module syn_asyn_rst(clk, rst, a, b,c); input clk; input rst; input a; output reg b,c; reg rst_n; always @(posedge clk) rst_n <= rst; always @ (posedge clk or negedge rst_n )// if (!rst_n) b<= 1'b0; else b <= a; always @ (posedge clk or negedge rst_n )// if (!rst_n) c<= 1'b0; else c <= b; endmodule

RTL:

各自的优缺点: