16.菜鸟初入FPGA之三态门

0赞

发表于 2016/4/15 下午8:31:10

阅读(8228)

三态指其输出既可以是一般二值逻辑电路的正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态(Hi-Z)。处于高阻抗状态时,输出电阻很大,相当于开路,没有任何逻辑控制功能。高阻态的意义在于实际电路中不可能断开电路。三态电路的输出逻辑状态的控制,是通过一个输入引脚 实现的

在之前的实验中,我们所接触到的 IO 都是单纯的输入( input) 或者输出(output)类型,而我们的一些总线协议如 IIC 等,要求信号为三态类型,也就是我们所说的输入输出( inout) 类型。接下来,我们就来看一下这类信号的具体用法,输入输出类型,顾名思义就是既可以作为输入,也可以作为输出

我们可以通过如下代码学习这类信号的赋值驱动方式

代码:

module state_3(clk,rst_n,sda); input clk,rst_n; inout sda; reg flag;//三态门开关 reg sda_buf;//待发送数据寄存器 assign sda = (flag == 1)?sda_buf : 1'bz; always @(posedge clk or negedge rst_n) if(!rst_n)begin flag <= 0; sda_buf <= 1; end else begin flag <= 1; end endmodule `timescale 1ns/1ns `define clock_period 20 module state_3_tb; reg clk,rst_n; wire sda; initial clk =1; always #(`clock_period/2) clk = ~clk; initial begin rst_n = 1'b0; #(`clock_period*5) rst_n = 1'b1; #(`clock_period + 1); #(`clock_period*200); $stop; end state_3 state_3(.clk(clk),.rst_n(rst_n),.sda(sda)); endmodule

rtl:

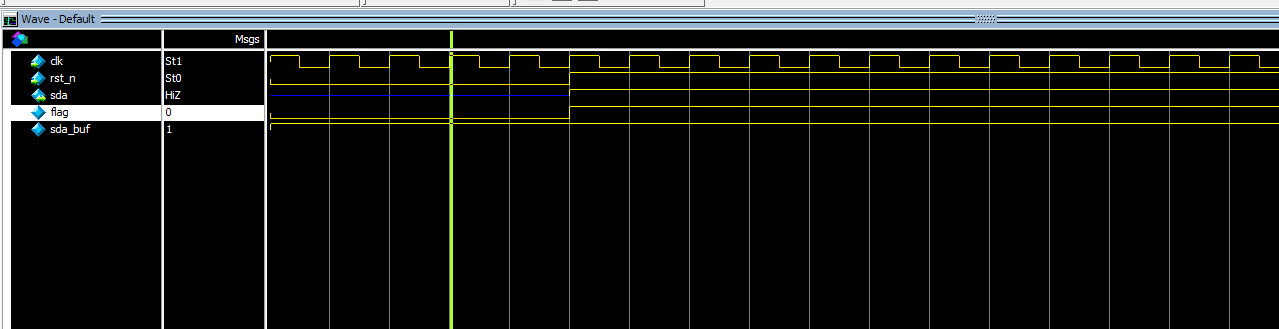

仿真:

典型的三态门应用:

如果你的设备端口要挂在一个总线上, 必须通过三态缓冲器。 因为在一个总线上同时只能有一个端口作输出, 这时其他端口必须在高阻态, 同时可以输入这个输出端口的数据。 所以你还需要有总线控制管理, 访问到哪个端口, 那个端口的三态缓冲器才可以转入输出状态。

更多资料请查看:

发烧友小梅哥专版

梦翼师兄炼狱传奇