FPGA中的竞争冒险消除

0赞竞争冒险消除

在FPGA的设计中,毛刺现象是长期困扰电子设计工程师的设计问题之,是影响工程师设计效率和数字系统设计有效性和可靠性的主要因素。由于信号在FPGA的内部走线和通过逻辑单元时造成的延迟,在多路信号变化的瞬间,组合逻辑的输出常常产生一些小的尖峰,即毛刺信号,也容易引起竞争冒险现象,从而使电路工作的稳定性大受影响。

1、竞争与冒险

1.1 竞争

说法1:门电路中有两个输入信号同时向相反的电平跳变的现象叫做竞争。

说法2:在组合电路中,某个变量(或信号)经过两条以上的路径到达输出端时,由于不同路径上的延迟时间不一样,达到输出端的时间就会有先有后,这一现象称作竞争。

如图所示电路及波形:对于与门,若稳态时,A=1,B=0或A=0,B=1时,输出皆为Y=0。但在信号的传输过程中,由于门的传输时间不同,造成在时间△t内,出现A和B同时高VIL(max),这样在输出端产生了很窄的脉冲,即Y=1,称为电压尖峰或电压毛刺。

1.2 冒险

在具有竞争可能的组合电路中,由于输入端的竞争而导致的输出端出现不该有的干扰脉冲(即所谓毛刺),就称为冒险。表现为输出端出现了原设计中没有的窄脉冲,常称其为毛刺。

冒险分类:

1)静态冒险与动态冒险

冒险按照其产生形式可以分为静态冒险与动态冒险。

静态冒险是指输入产生变化时输出产生单个窄脉冲的现象。静态冒险按其稳态与尖峰的不同可以分为静态0型冒险与静态1型冒险。静态1型冒险是指电路稳态输出均为1,在输入信号变化时产生短暂的0脉冲的现象。静态0型冒险正好相反。

动态冒险是指由于输入变化而导致的输出产生变化的现象,换言之,就是由于发生了多次静态冒险导致输出多个窄脉冲的现象。静态冒险是由于信号变化存在快慢而导致,而动态冒险是由于静态冒险而导致的,当电路中存在快、慢与更慢的电路时,就会产生动态冒险,因为当不同速度的信号变化组合时,就会产生多个窄脉冲。

2)逻辑冒险和功能冒险

冒险按照其产生条件,可以分为逻辑冒险和功能冒险两大类。

逻辑冒险是指电路中只有一个信号发生变化却导致了输出产生冒险的现象。顾名思义,这是由于电路的逻辑设计的不合理导致,因此应该避免此现象,也就是避免下面所说的代数法中的问题。

功能冒险是指由于电路中两个或者以上的信号发生变化时,由于电路和器件本身的特性导致的到达时间差而产生的冒险。功能冒险较之于逻辑冒险更难处理。

1.3 竞争与冒险的关系

有竞争不一定会有冒险,但有冒险就一定有竞争。

1.4 检查竞争冒险的方法

1)逻辑表达式化简法

如果输出端门电路的两个输入信号A和A’是输入变量A经过两个不同的传输途径而来,则当输入变量发生变化时,输出端就可能产生尖峰脉冲。

故对于输出端的逻辑函数在一定条件下能化简成:

Y=A+A’ , 存在 “0” 型竞争;

Y=A*A’ , 存在 “1” 型竞争;

的情况下,则判定一定有竞争冒险现象。

2)卡洛图法

即如果一个逻辑函数的表达式的卡洛图中所画圈没有重叠并且相切,则判定有竞争冒险。(本质上还是利用上面的方法,只是比较直观形象的判断)

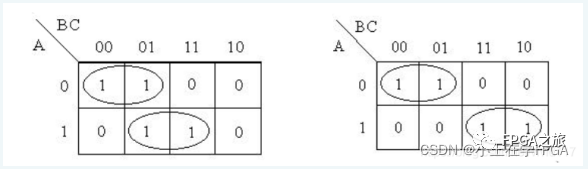

对于以下卡洛图,左图存在竞争冒险,而由图不存在竞争冒险。

具体方法:

通过逻辑表达式画出卡诺图来判断是否会出现冒险现象,当卡诺图中的卡诺圈相切,则有竞争冒险。

由上图,图中的圈称为卡诺圈,卡诺圈中只能包含1,2,4,8....2^n(n为非负整数)个元素,当该函数在A=B=1时,存在0型逻辑冒险。

图中红圈与蓝圈有相切的地方,被称为卡诺圈相切。

1、变量取值在卡诺圈内变化,不存在逻辑冒险;

2、变量取值在相切的卡诺圈跳变时,而这个相切部分又没有被另外的卡诺圈包围,则可能存在逻辑冒险。

1.5 消除竞争冒险的措施

FPGA设计中最简单的避免方法是尽量使用时序同步逻辑同步输入输出。

(a) 修改逻辑设计,增加冗余项,消除逻辑冒险;

1)存在竞争的情况下,增加冗余项,实现输出消除毛刺。

例:逻辑表达式如下:Y = A’BC + AB

当B = C = 1时, 电路存在“0”型竞争。增加项:冗余项 B&C

更变后:Y = A’BC + AB + B C (利用消去冗余项公式)

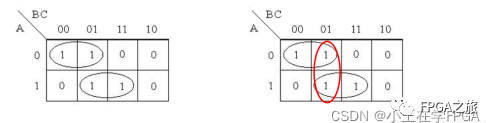

2)还有卡诺图法,在两个相切的圆之间,相切接触的地方增加一个连接圆。

对于上面的卡洛图,在相切的位置增加 冗余项 B’C,故函数表达式Y=A’B’+AC+B’C

(b)采用可靠性编码,如格雷码;

(c)引入旁路滤波电容,输出并联滤波电容消除毛刺;

在输出端并联接一个很小的滤波电容,削弱尖峰脉冲的幅度至门电路的阈值以下。简单易行,但是会增加输出电压波形上升时间和下降时间,使波形变坏。

(d)加封锁脉冲;

即在输入信号产生竞争冒险的时间内,引入一个脉冲将可能产生尖峰干扰脉冲的门封锁住,封锁脉冲应该在输入信号转换前到来,转换后消失。

(e)加选通脉冲;

即对输出可能产生尖峰脉冲的门电路增加一个接选通信号的输入端,只有在输入信号转换完成并稳定后,才引入选通脉冲将它打开,此时才允许有输出。

For逻辑冒险:增加冗余项(得到非最简逻辑,属于修改逻辑设计的方法);卡诺图法;增加选通电路;增加输出滤波电容。由此看出,两面性来了:一方面想最简化逻辑电路,可是却有可能出现竞争冒险,退而求其次,则恰当解决问题。

For功能冒险:功能冒险是由于在输入n个变量同时变化时,它们的实际变化在时间上有先有后引起的,因此改变电路的逻辑设计并不能消除功能冒险。对待功能冒险常用的方法是增加选通信号或者增加输出滤波电容方法。

2、毛刺

2.1 毛刺产生的原因

①建立时间和保持时间

建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器,如图所示,数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

②竞争和冒险

FPGA芯片是由可构造的输入输出块(Input/Output Block,IOB)、可构造逻辑块(Cinfigurable Logic Block,CLB)和可编程连线资源(Programmable Interconnect Array,PIA)3种可构造单元构成的。IOB位于芯片内部四周,在内部逻辑阵列与外部芯片封装引脚之间提供一个可编程接口,他主要由逻辑门、触发器和控制元组成。CLB组成了FPGA的核心阵列,能完成用户指定的逻辑功能;每个CLB主要有一个组合逻辑、几个触发器、若干个多选一电路和控制单元组成;PIA位于芯片内部的逻辑块之间,经编程后形成连线网络,用于芯片内部逻辑间的相互连接,并在他们之间传递信息。信号在FPGA器件内部通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、 工作电压、温度等条件的影响。信号的高低电平转换也需要一定的过渡时间。由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑 的输出有先后顺序,并不是同时变化(及竞争现象),往往会出现一些不正确的尖峰信号,这些尖峰信号称为"毛刺"。如果一个组合逻辑电路中有"毛刺"出现,就说明该电路存在"冒险"。(与分立元件不同,由于PLD内部不存在寄生电容电感,这些毛刺将被完整的保留并向下一级传递,因此毛刺现象在PLD、FPGA设计中尤为突出)也就是说,在FPGA设计中,毛刺产生的根本原因是信号在芯片内部走线时产生的延迟。

2.2 毛刺产生的条件

由于延迟的作用,多个信号到达终点的时间有先有后,形成了竞争,由竞争产生的错误输出就是毛刺。所以,毛刺发生的条件就是在同一时刻有多个信号输入发生改变。

2.3 毛刺的危害

当毛刺信号成为系统的启动信号,控制信号,握手信号,触发器的清零信号,预置信号,时钟信号,或锁存器的输入信号时就会产生逻辑错误。

2.4 消除毛刺的方法

知道了毛刺产生的条件,就可以通过改变设计,破坏其条件来减少毛刺的发生。例如,利用格雷码计数器每次输出只有一位跳变的特性,代替普通的二进制计数器,避免了毛刺的产生。还可以对电路进行改进,以消除毛刺对系统的影响。

①利用冗余项法

利用冗余项消除毛刺有2种方法:代数法和卡诺图法,两者都是通过增加冗余项来消除险象,只是前者针对于函数表达式而后者针对于真值表。以卡诺图为例,若两个卡诺圆相切,其对应的电路就可能产生险象。因此,修改卡诺图,在卡诺图的两圆相切处增加一个圆,以增加多余项来消除逻辑冒险。但该法对于计数器型产生的毛刺是无法消除的。

②采样法

由于冒险多出现在信号发生电平跳变的时刻,即在输出信号的建立时间内会产生毛刺,而在保持时间内不会出现,因此,在输出信号的保持时间内对其进行采样,就可以消除毛刺信号的影响,常用的采样方法有2种:一种使用一定宽度的高电平脉冲与输出相与,从而避开了毛刺信号,取得输出信号的电平值。这种方法必须保证采样信号在合适的时间产生,并且只适用于对输出信号时序和脉冲宽度要求不严的情况。另一种更常见的方法叫锁存法,是利用D触发器的输入端D对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输出信号。由于在时钟的上升沿时刻,输出端Q=D,当输入的信号有毛刺时,只要不发生在时钟的上升沿时刻,输出就不会有毛刺。这种方法类似于将异步电路转化为同步电路,实现简单,但同样会涉及到时序问题。

③吸收法

由于产生的毛刺实际上是高频窄脉冲,故增加输出滤波,在输出端接上小电容C就可以滤除毛刺。但输出波形的前后沿将变坏,在对波形要求较严格时,应再加整形电路,该方法不宜在中间级使用。

④延迟法

因为毛刺最终是由于延迟造成的,所以可以找出产生延迟的支路。对于相对延迟小的支路,加上毛刺宽度的延迟可以消除毛刺。但有时随着负载增加,毛刺会继续出现,而且,当温度变化,所加的电压变化或要增加逻辑门时,所加的延迟是不同的,必须重新设计延迟线,因而这种方法也是有局限性的。而且采用延迟线的方法产生延迟会由于环境温度的变化而使系统可靠性变差。

⑤硬件描述语言法

这种方法是从硬件描述语言入手,找出毛刺产生的根本原因,改变语言设计,产生满足要求的功能模块,来代替原来的逻辑功能块。

在Verilog编程时,需要注意以下几方面,在绝大多数情况下可避免综合后仿真出现冒险问题。

1)时序电路建模时,用非阻塞赋值。

2)锁存器电路建模时,用非阻塞赋值。

3)用always和组合逻辑建模时,用阻塞赋值。

4)在同一个always块中建立时序和组合逻辑模型时,用非阻塞赋值。

5)在同一个always块中不要既使用阻塞赋值又使用非阻塞赋值。

6)不要在多个always块中为同一个变量赋值。

避免在综合时引入锁存器的注意点包括:

1)组合电路的每一个if-else语句要完整,即每一个if要对应一个else,时序电路if语句不完整不会出现锁存器问题。

2)case语句要完整,即每一个case语句对应一个default。

原文链接:https://mp.weixin.qq.com/s/f1ynyCmMA0i32hTPYk25OA

电子技术应用专栏作家 FPGA之旅