modelsim的TCL脚本的define incdir命令使用方法

1赞 做FPGA开发的,学会熟练使用modelsim,可以高效的完成开发任务。如果能熟悉一些在modelsim中常用的TCL命令,则可以更方便、更高效的完成代码的开发任务。下面简要介绍两个TCL命令:

(1) +incdir+:

如:vlog +incdir+YOUR_SOURCE_PATH foo.v

+incdir+YOUR_SOURCE_PATH 选项是指在verilog文件中出现`include "xxx.v" 时,包含文件的搜索路径。

缺省是搜索当前路径,然后是YOUR_SOURCE_PATH 指定的路径。

(2) +define+:

+define+<macro_name>[=<macro_text>]

允许用户在命令行中定义宏定义,等效于编译器指令:

`define <macro_name> <macro_text>

用户可以指定多个宏定义,如下:

vlog +define+one=r1 +two=r2 +three=r3 test.v

命令行的宏定义会覆盖在源文件中用`define定义的相同名字的宏定义

如:vsim -c -l vsim.log -do ./YourDo.do -L ./work work.foo

开始仿真:

-c 选项让vsim工作在commandline模式;

-l 选项是输出log文件到vsim.log;

-do 选项是开始仿真后运行tcl脚本文件;

-L 选项是指定工作逻辑库;

work.foo是仿真的top level module。

举例说明:

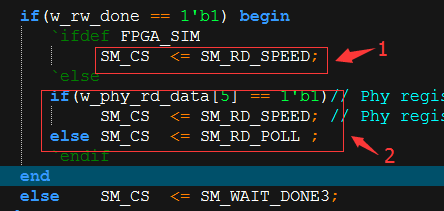

当我们在代码中,设置了条件编译,如下:

在这里,如果代码是用于仿真,则希望执行第一部分;如果是用于综合生成实际的可执行文件,则希望执行第二部分。这时,我们就可以使用上面的写法来写代码,但是在该文件中可以不写“FPGA_SIM”的宏定义。

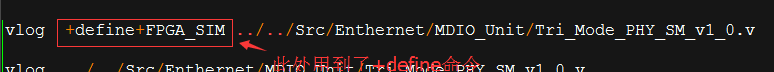

然后用modelsim仿真该文件时,使用下面的方法添加该文件的路径,则执行第一部分(即“SM_CS <= SM_RD_SPEED”):

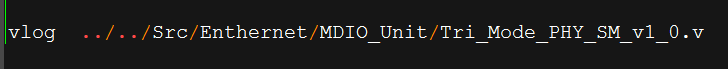

如果使用下面的方法添加该文件的路径,则执行第二部分:

PS:基于FPGA的视频编解码QQ群:623495899 ,有兴趣的可以进来交流学习哈。