【原创】LinCoding告诉您什么才是IO口

1赞【主题】:LinCoding告诉您什么才是IO口

【作者】:LinCoding

【时间】:2016.11.8

【声明】:转载、引用,请注明出处

连续一周了,在弄传说中的SDRAM,不是说SDRAM,有多么多么难,我是受友晶SDRAM封装库的启发,想写一个通用版的SDRAM程序,更换SDRAM时候只需要改行列,就可以直接使用,虽然从上上周日开始看了一周友晶的SDRAM库,看懂了,并且自己写了全部的注释,但是移植到我黑金板子上时候,怎么都成功不了,各种找问题,实在是找不到,所以,从上周开始,打算自己写一个SDRAM的驱动程序,前前后后看SDRAM有10天了,真的是把我弄的寝食难安,觉睡不好,女票陪不了,不过这10天看了很多很多网上关于SDRAM的资料什么的 ,算是快把SDRAM吃透了,现在写好了单字节读写的程序,并且在两个不同芯片,不同SDRAM的FPGA上试了,可以很方便移植,等我整个写好以后,会免费上传到我的博客里,需要的朋友可以免费下载。

好了,废话说了一大推,在仿真SDRAM时候,由于SDRAM的数据口是inout型,那么,仿真时候该怎么弄呢,网址可能有人有过总结,但是我还是写一下吧,顺便谈谈我对IO口的理解。

一、什么是IO口

这还用说,就是既能做输入,又能做输出呗,所谓Input output的首字母缩写

二、什么是双向IO口,什么准双向IO口

是不是感觉。。。一下答不上来,反正笔者曾经是这样,不过各位大神一定对答如流了。

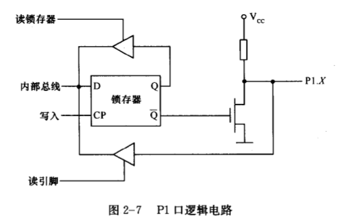

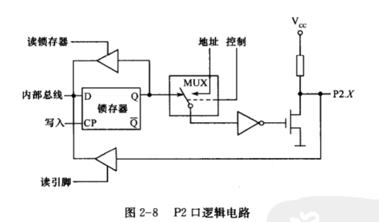

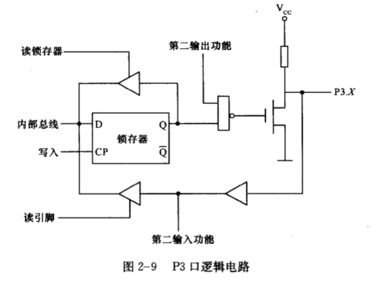

在学习标准51单片机时候,大家可能都知道,或者听过,或没注意过51单片机的IO口分为双向和准双向,具体起来说,就是80C51的P1、P2和P3为准双向IO口,P0为双向IO口,在学习STM32时候,更为恐怖,又是推挽,又是上拉,下拉的。。。整的刚开始学习的笔者直接懵逼了。。。,但是道理上都是一样的。那么问题来了什么是准双向?什么是双向?

“要读取时候先输出1,才能读,为准双向”,课本上是这么说的,但是说的好像P0口读取时候不用输出1一样,其实这并不是这么简单。

以下为笔者个人的理解:如果有误,笔者可不负责任啊,哈哈,倒是可以相互交流。

先看看51单片机IO的结构吧:

上面4副图引用自:《从零开始学单片机技术》——刘建清

这本书在讲51的IO结构时候说的还算比较清楚的,想弄清楚的读者,建议看一下。笔者看过有的书都是一笔带过,有的没怎么说清楚。

笔者理解如下:

P0口之所以称之为双向IO口是因为在作为地址/数据功能时,构成了推挽结构,可输出高电平和低电平,且当上下两个MOS管都截止时,呈现高阻态,可以实现内外数据的隔离,当PO口作为普通IO口使用时,构成了OC/OD门,即开集电极/漏极输出,低电平可以正常输出,但如果要输出高电平,必须外加上拉电阻。作为输入时,必须先输出1,即向内部的锁存器写1,以断开下拉的MOS管,此时,管脚处于浮空状态,然后读引脚就可读入高低电平。

P1、P2、P3之所以称之为准双向IO口,是因为内部带了上拉电阻,因此在任何时候都不会出现高阻态,只会出现高低电平。作为输出时,可输出高低电平,作为输入时,必须先输出1,即向内部的锁存器写1,以断开下拉的MOS管,然后读引脚就可读入高低电平。

准双向IO口输出低电平时,灌电流可达20mA,输出高电平时,输出能力较弱,不到1mA,若到输出高电平给其他器件,由于其他器件输入时为高阻态,因此可正常将高低电平输出,但,若要驱动外设(如LED),最好通过控制三极管来达到控制外设的效果。

说了这么多,晕了吧。。。。那就说简单点:

凡是在输出状态下能输出高电平和低电平,在输入状态下可以呈现浮空(高阻)的门即为三态门,它所构成的IO口成为双向IO,除此之外其他IO都是准双向IO。所以说只要能出现三态情况的口都是为双向口,只能出现两态的就叫准双向了呗。

虽然不知道笔者总结的对不对,但是在做SDRAM的数据口仿真时候,没有与现有的资料冲突

三、如何驱动或仿真带有IO口的模块

1、IO口驱动(只截取最重要的)

inout [15:0] IO; input [15:0] WR_data; output reg [15:0] RD_data; reg isOut; always @ ( posedge CLK or negedge RSTn ) begin if ( ! RSTn ) isOut <= 1'b0; else case ( state ) 0: // read data from IO begin isOut <= 1'b0; RD_data <= IO; state <= state + 1'b1; end 1: // write data to IO begin isOut <= 1'b1; state <= state + 1'b1; end endcase end assign IO = isOut ? WR_data : 16'dz;

2、IO口仿真(只截取最重要的)

reg [15:0] treg_IO; // read IO wire [15:0] IO; // Write IO assign IO = treg_IO; reg [15:0] RD_data; reg [15:0] WR_data; always @ ( posedge CLK or negedge RSTn ) begin if ( ! RSTn ) rData <= 0; else case ( state ) 0: // read data from IO begin RD_data <= IO; state <= state + 1'b1; end 1: // write data to IO begin treg_IO <= WR_data; state <= state + 1'b1; end endcase end