安路FPGA初用

0赞原计划这篇文是要在年前写完,不好意思,跳了个票。

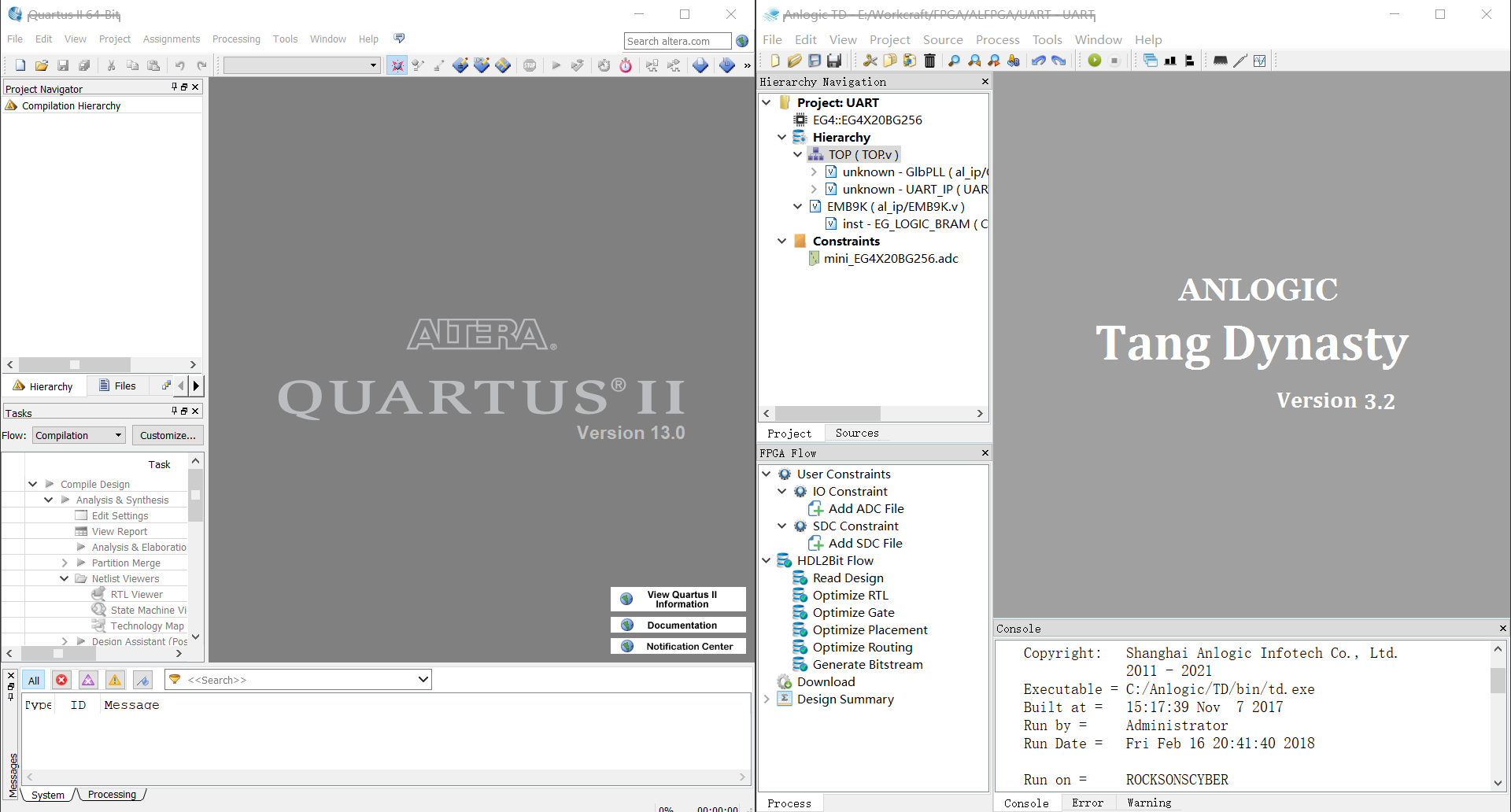

首先第一眼看上去就界面上确实是很像Quartus。。。

使用的一些感觉/遇到的问题:

软件稍简陋些,但不是什么大问题。基本上读一读软件的手册问题都能得到解决。

软件在进入一些子介面的时候似乎总是有点卡,比如IP生成器,总是会卡上一会儿。

IP核生成器里的IP核好像太少了。。。

Bug:在关闭工程时,如果此时IO编辑界面没有关闭,程序会崩溃。

有点反人类的地方:软件里有很多地方的Yes/No是反的,比如:

然后说一下我最近都耗在了什么东西上:

我之前自己写了一个UART,其实现在想想调试过程挺搞笑的,盲人摸象一般照着网上资料敲了两个状态机出来,一个管发送,一个管接收,共用一个波特率发生模块作为时钟输入。想着写到不报错,在Quartus里用VWF+功能仿真过,能生成bitstream,烧进FPGA直接试试就完了。

然后理所当然的遇到了一大堆问题

预置了数据,Tx和Rx接到一起,高7位没啥问题,第1位永远是低电平,这是用Quartus9自带的功能仿真的时候始终无法复现的现象。。。后来光查这个查了老长时间。。。。某天不知和同学聊到啥话题的时候突然想到会不会是延时的问题。在Quartus自带仿真中使用时序仿真后复现错误。

某种意义上犯得最智障最搞笑的错误,计算按照11.0592MHz的输入频率在波特率发生模块里填计数值,然后生成PLL的时候填了一个5MHz进去,无论怎么选波特率,收发都不正常。怀疑自己代码出问题很长时间查不出头绪。

UART这玩意给个过采样还是非常非常有必要的,被网上很多用简单状态机完成接收的资料带到沟里了。

就先说这么多吧。。。水平依旧too young too simple,sometimes Naive。还是有很多东西要学啊。。。至少说,testbench都不会写怕是说不过去啊。