基于FPGA的多功能数字时钟设计

3赞新手,第一次写博客,感觉作为工程师不仅仅要能够在项目的设计上展现自己的专业技能,还要能够为设计做出详细的解释与说明,通过与众多网友的交流沟通,完善自己的缺点,更能结识到志趣相投的朋友,所以我觉得写博客是一个很好的提升自己的方式,作为菜鸟的我通过写博客分享我的心得既可以检测自己是否真正对此设计了然于胸,也能锻炼写文档的技能,说不定还能得到哪位大神的指点,真的是收获颇多的,所以以后就一定要坚持写博客。这次毕竟是第一次写,感受相当的多,心情也很激动,废话不多说,下面就进入正题吧~

***********************************************************************************************************

设计题目:基于FPGA的多功能数字时钟设计

开发环境:ISE 14.7

开发板:BASYS 2

简介:本设计是基于FPGA的多功能数字时钟,使用Xilinx公司的BASYS 2开发板实现,利用BASYS 2开发板上的拨码开关和独立按键作为控制输入,LED和数码管作为显示输出,可以实现秒表、时钟、闹钟和计时器功能

*设计成果

基本功能:

(1) 秒表:复位时,时钟的时、分、秒都为零,关闭复位后,秒开始计时。

(2) 可调节时钟:打开暂停开关,关闭复位后,就进入调节模式,通过按键可对时、 分、秒及厘秒进行

调节,调整好后,关闭暂停开关,就进入了时钟模式。

扩展功能:

(1) 闹钟:在调节模式时,通过按键设定闹钟启动的时间,打开寄存开关后,再关闭,此时闹钟以设定

好,时钟模式下,到达设定的闹钟时间时,会有一分钟的LED流水灯提示。

(2) 计时器:在调节模式时,通过按键设定计时的时间,然后打开计时器模式开关,关闭暂停开关,就进

入了倒计时模式。

*方案设计

1,数码管显示

采用数码管分别显示时钟的时、分、秒和厘秒,但因为BASYS 2 开发板上只有四个数码管,而时钟一共有八位,需要八个数码管,所以我加入了一个按键切换功能,小时和分钟为一个显示界面,秒钟和厘秒钟(比秒更小的单位,精度为0.01秒,为了方便,自己起的名字~haha)为一个显示界面,我们只要控制数码管的位选端和段选端使数码管显示时钟的数字即可,复位时,全部清零,复位后,进行时钟样式显示。

2,设置计数器(这里我采用时钟的每一位对应一个计数器的方法)

2.1 基础计数器(作为时钟每一个计数器的基础,即最小时间单位)

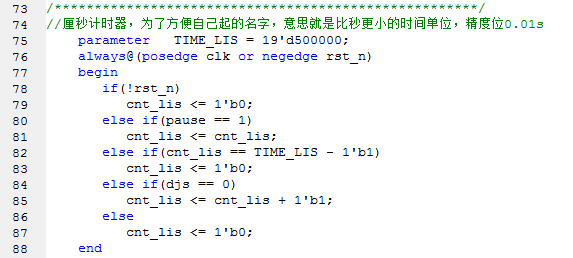

(1)厘计数器cnt_lis:控制厘秒,精度0.01s。

(2)一秒计数器cnt_1s:控制时、分、秒,精度1s。

2.2时、分、秒和厘秒计数器

(1)厘个位cnt_li_ge:

初值:0

加1条件:cnt_lis == 500000 - 1

最大值:9

(2)厘十位cnt_li_shi:

初值:0

加1条件:cnt_lis == 500000 - 1 && cnt_li_ge == 9

最大值:9

(3)秒个位cnt_miao_ge:

初值:0

加1条件:cnt_1s == 50_000_000 - 1

最大值:9

(4)秒十位cnt_miao_shi:

初值:0

加1条件:cnt_1s == 50_000_000 - 1 && cnt_miao_ge == 9

最大值:5

(5)分个位cnt_fen_ge:

初值:0

加1条件:cnt_1s == 50_000_000 - 1 && cnt_miao_ge == 9

&& cnt_miao_shi == 5

最大值:9

(6)分十位cnt_fen_shi:

初值:0

加1条件:cnt_1s == 50_000_000 - 1 && cnt_miao_ge == 9

&& cnt_miao_shi == 5 && cnt_fen_ge == 9

最大值:5

(7)时个位cnt_shi_ge:

初值:0

加1 条件:cnt_1s == 50_000_000 - 1 && cnt_miao_ge == 9

&& cnt_miao_shi == 5 && cnt_fen_ge == 9

&& cnt_fen_shi == 5

最大值:cnt_shi_shi == 0 || cnt_shi_shi == 1时,为9

cnt_shi_shi == 2时,为3

(8)时十位cnt_shi_shi:

初值:0

加1条件:cnt_1s == 50_000_000 - 1 && cnt_miao_ge == 9

&& cnt_miao_shi == 5 && cnt_fen_ge == 9

&& cnt_fen_shi == 5 && cnt_shi_ge == 9

最大值:2

清零条件:cnt_1s == 50_000_000 - 1 && cnt_miao_ge == 9

&& cnt_miao_shi == 5 && cnt_fen_ge == 9

&& cnt_fen_shi == 5 && cnt_shi_ge == 3

&& cnt_shi_shi == 2

3 ,译码显示电路

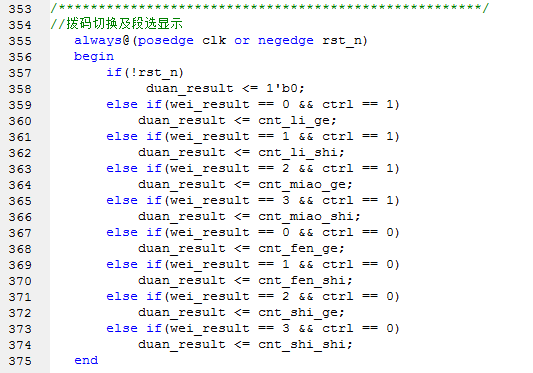

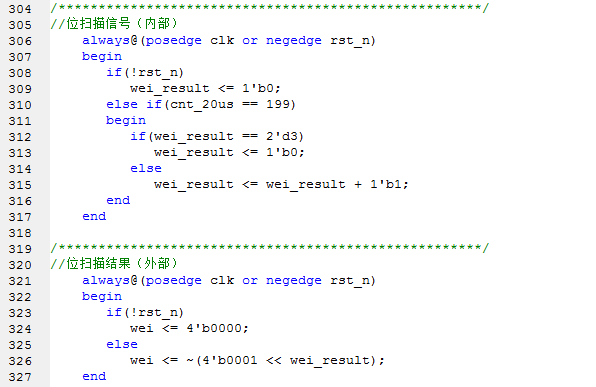

将时、分、秒等数值转化为数码管显示,先选择,再译码,节省FPGA资源,因为BASYS 2开发板只提 供4个数码管,故可设置一个切换信号ctrl, 当ctrl == 0时,4个数码管分别显示时十位、时个位、分十位、分个位当ctrl == 1时,4个数码管分别显示秒十位、秒个位、厘十位、厘个位。

4 ,数码管选择电路

用于动态扫描,扫描周期20us,故需要设计一个计时20us的计数器cnt_20us, 每隔20us,数码管位选端依次变换一个。

5 ,秒表功能

复位时,数码管全部清零;复位后,进行时钟样式显示,厘秒开始计数,此时处于秒表功能模式。

6 ,暂停功能

电路包含两个状态,计时和暂停,故需要一个信号来指示,设信号 pause == 0,表示计时,pause == 1,表示暂停。当pause == 1时,让计数器cnt_1s和cnt_lis停止计数,即可达到时钟暂停的目的;当pause == 0时,让计数器cnt_1s和cnt_lis继续计数,即可达到时钟继续计数的目的,故采用拨码开关控制暂停信号,高电平暂停,低电平计数。

7, 时钟调节功能

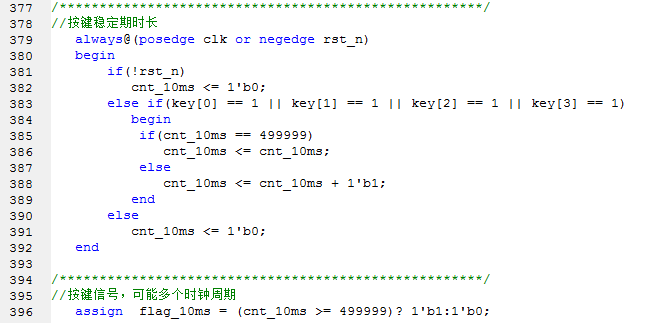

BASYS 2开发板提供四个独立按键,故可以用四个按键对八个时钟计数器进行调节,在计数器暂停状态时,复位后,即进入调节模式,按一下按键key, 对应的时钟计数器加1,设按键信号 key_en,当按下按键时,key_en ==1,一个系统时钟周期过后,key_en == 0,时钟计数器检测到key_en == 1,就执行加1的操作,否则保持不变,调节好时钟后,恢复计时状态,此时处于时钟模式。

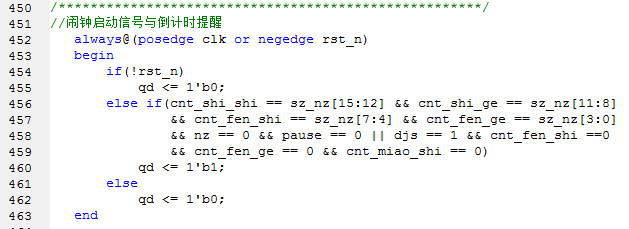

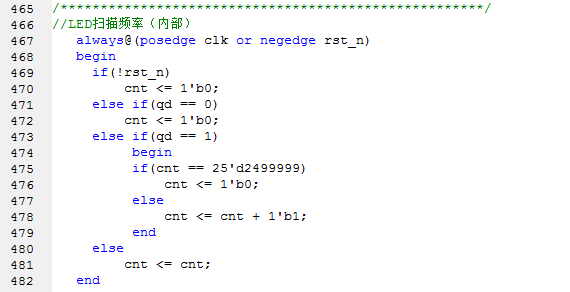

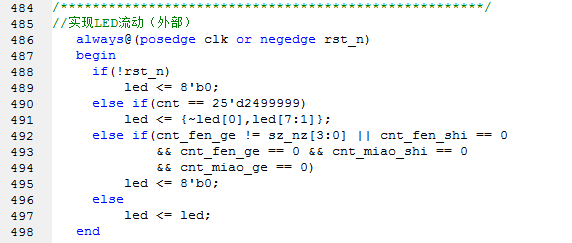

8, 闹钟功能

设置闹钟信号nz,在调节模式时,调好闹钟时间,让闹钟信号nz处于高电平,即可将调节好的闹钟时间储存在闹钟寄存器sz_nz中,然后恢复闹钟信号nz为低电平,时钟模式时,到达预设的闹钟时间,启动led流水灯,一分钟过后,流水灯熄灭。

9 ,计时器功能

设置计时器信号djs,在调节模式时,调好计时器的倒计时时间,让计时器信号djs处于高电平的状态下,恢复暂停信号,则进入倒计时模式,倒计时进入最后十秒时,启动led流水灯,提醒倒计时时间,倒计时结束

后,Led流水灯自动关闭。

*结果测试

各个功能都能正常进行,拨码开关和独立按键作为输入,能够较准确的控制各个信号有条不絮的进行;led和数码管作为输出,在输入信号的控制下,也能较准确的显示各个功能。不足的是,由于对verilog语法掌握的不够完善,整体框架不够紧凑,对FPGA设计的模块化思想不够熟练,也导致浪费一些FPGA资源,在以后的设计中,要着重把握这些。

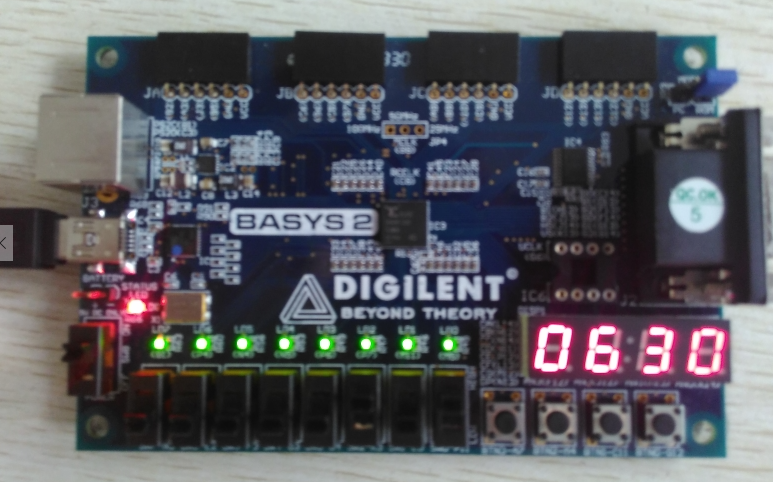

下面是实物图:

此时显示的是12:30

6:30分的闹钟,LED闪烁提醒

倒计时最后10秒时,LED闪烁提醒

由于时间和地方的限制,这里的代码并不完善,如若有兴趣,可以点击下面的链接查看完整工程,包括源代码和注释都很详细,如果有不正确的地方还请大神指点,必当感激不尽!

百度云链接 ---->基于FPGA的多功能数字时钟设计(完整工程)

技术只有多交流才能进步的更快,在此希望有共同爱好的网友能够和我一起探索FPGA的奇妙世界,一起学习,共同进步~!

欢迎留言探讨~