PCIe从入门到精通之一:综合简介

0赞0,引言

PCIe是硬件工程师跨不过去的坎。我刚开始工作就接触PCIe,工作中遇到的所有产品都有PCIe总线。在此想把自己学习PCIe的一些经历和感悟,以及踩过的坑分享在这里,与大家一起进步。所有PCIe主题的文章都会收录在《深入浅出聊PCIe》合集里,每篇文章一个PCIe的主题,预计会有几十章节。

让我们从零开始的了解PCIe,一步一步深入。

需要下载PCIe学习资料标准的朋友(pdf格式),请关注本微信公众号“硬件工程师宝典”,在对话框内回复“PCIe”,将获取标准下载链接。

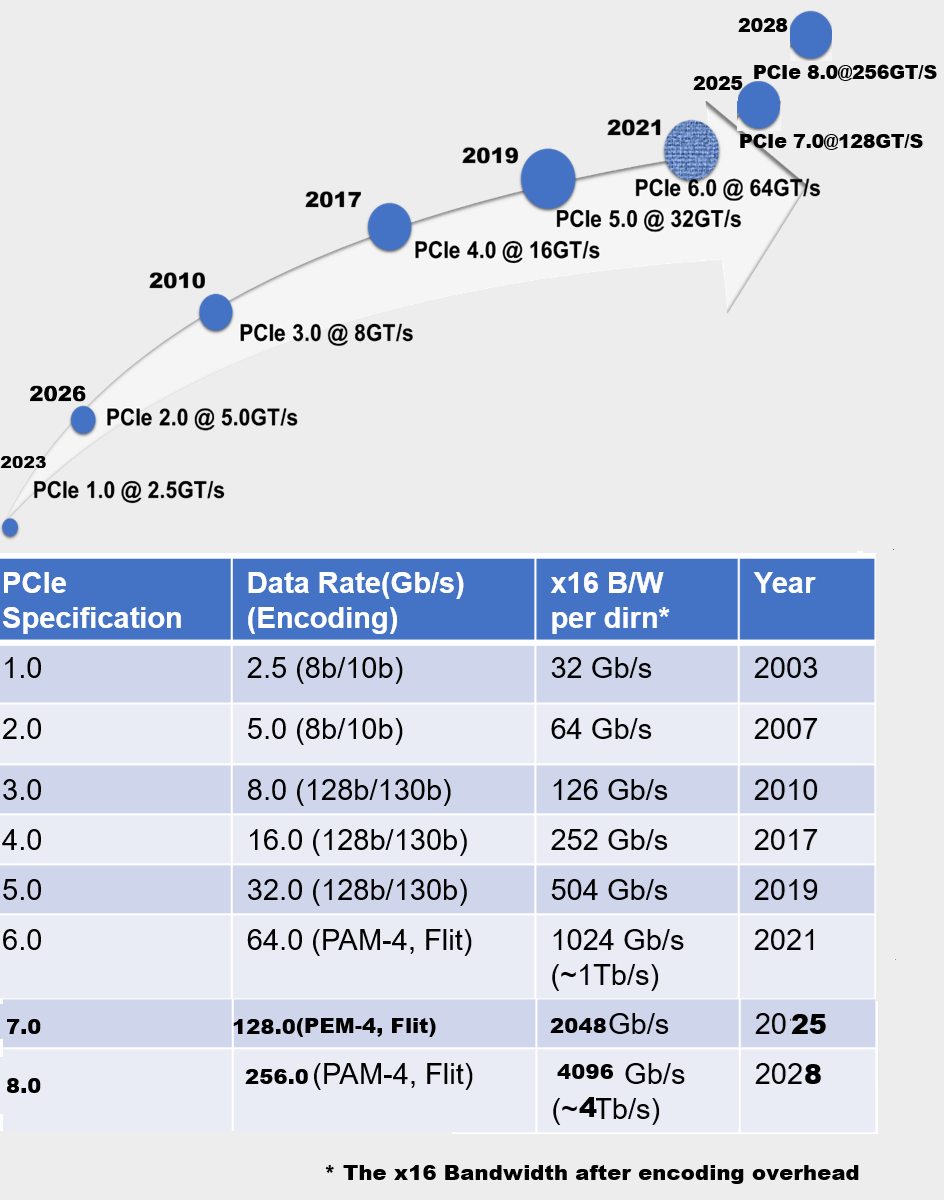

开局一张图,后面的内容全靠它。

备注:上图中的x16 B/W是考虑编码损耗以后的单向数据带宽。

一,PCI总线的硬伤

上古时期,诸神发明了PCI总线(PCI于1992年推出,那时的我刚好可以打酱油了。)。它是计算机与周边设备互联的主要接口。32位PCI总线,33 MHz时钟频率:这是最常见的PCI版本(也有更高的速度),其峰值传输速率为 133 MB/s。 (33.33 MHz × 32 bits ÷ 8 bits/byte = 133 MB/s)。

PCI总线有各种硬伤,主要表现为:

1. “排队等候”是常态:所有的公司(设备)要发快递,都得挤到这条单行道上。你想啊,显卡要发个高清视频数据,硬盘要读写个大文件,声卡要播放个音乐,大家都在这条道上排队。谁先谁后?那可就得看运气了。结果就是,明明你的显卡很牛,但数据传输可能还得等硬盘那边的文件读完,效率那叫一个“感人”。

2. “限速”是硬伤:这条单行道不仅容易堵车,它的最高限速也比较低。在那个年代,200多MB/s的传输速度已经算不错了,但随着显卡越来越强大,数据量越来越大,这条道就显得越来越窄,完全跟不上时代发展的步伐。

3. “并行”的烦恼:PCI采用的是并行传输,就像很多条细线并排传输数据。听起来很厉害,但问题是,当速度快起来的时候,这些细线上的信号很容易互相干扰,导致数据出错。这就好比你和一群朋友在一条狭窄的走廊里并排跑,跑快了就容易撞到一起,甚至摔跤。

二,“后辈”PCIe横空出世

实际的需求催生了技术的变革。 PCIe就像是计算机王国里的一场“交通革命”,它彻底解决了PCI时代“堵车、限速、信号差”的顽疾,让各种硬件设备能够真正发挥出它们的“洪荒之力”。PCI老前辈呢,也光荣地完成了历史使命,退出了主流舞台。

PCIe(全称:Peripheral Component Interconnect Express),中文常译作“高速外围组件互连”,你可以把它理解成计算机上各种硬件设备之间的一条点对点连接的“高速铁路”。通过这条“高速铁路”,各种不同的硬件设备之间可以传输数据。

它的主要作用是什么?

在计算机里,中央处理器(CPU)需要和GPU、固态硬盘(SSD)、网卡、声卡、BMC、FPGA、ASIC等各种硬件进行数据交换才能协同工作。PCIe就是专门用来连接这些设备,让它们之间能够高效、快速地传输数据,就像不同城市之间的高速铁路一样,它连接在不同的城市之间进行数据的高速传输。

三, PCIe标准的迭代和速度

再回到下面的这张图,重要的事情要说三遍。

· PCIe 1.0:

发布时间:2003年。

特点:作为PCI Express技术的首个标准,它标志着从传统并行PCI总线向串行互联架构的转型。 PCIe 1.0a的单通道(Lane)数据速率为2.5 GT/s,采用8b/10b编码,单通道带宽约为250 MB/s。

· PCIe 2.0:

发布时间:2007年初。

特点:传输速率在PCIe 1.x的基础上翻倍,每通道速率达到5 GT/s,单通道带宽提升至500 MB/s,x16配置下总吞吐量达到8 GB/s。

· PCIe 3.0:

发布时间:2010年11月。

o 特点:数据速率提高到8.0 GT/s。 最大的改变是采用了更高效的128b/130b编码机制,将编码开销从20%降低到1.5%,使得每个引脚的带宽比PCIe 2.0翻了一番。

· PCIe 4.0:

发布时间:2017年10月。

特点:数据速率从8.0 GT/s翻倍到16.0 GT/s,单通道带宽约2 GB/s,x16配置下总吞吐量达到64 GB/s。 PCIe 4.0保留了128b/130b编码方案。

· PCIe 5.0:

发布时间:2019年5月。

特点:传输速率再次翻倍,达到32 GT/s,x16配置下可提供128 GB/s的吞吐量。

· PCIe 6.0:

发布时间:2022年1月。

特点:传输速率翻倍至64 GT/s,x16配置下可提供256 GB/s的总吞吐量。 PCIe 6.0首次引入了脉冲幅度调制PAM4信号编码,使得在保持信道带宽不变的前提下,实现了传输速率的翻倍。 它还引入了低延迟前向纠错(FEC)和固定大小的FLIT(流量控制单元)编码。

· PCIe 7.0:

发布时间:PCI-SIG已于2025年6月11日正式发布PCIe 7.0规范。

特点:旨在将传输速率从PCIe 6.0的64 GT/s提升一倍至128 GT/s,通过x16配置可提供高达512 GB/s的双向传输速度。

· PCIe 8.0:

PCIe 8.0 规范的目标是达到 256.0 GT/s(通过 x16 配置双向可达 1.0 TB/s),计划于 2028 年向成员发布。

PCIe标准的每一次迭代都致力于在提高数据传输速度和带宽的同时,优化延迟和效率,并保持与前几代技术的向后兼容性。

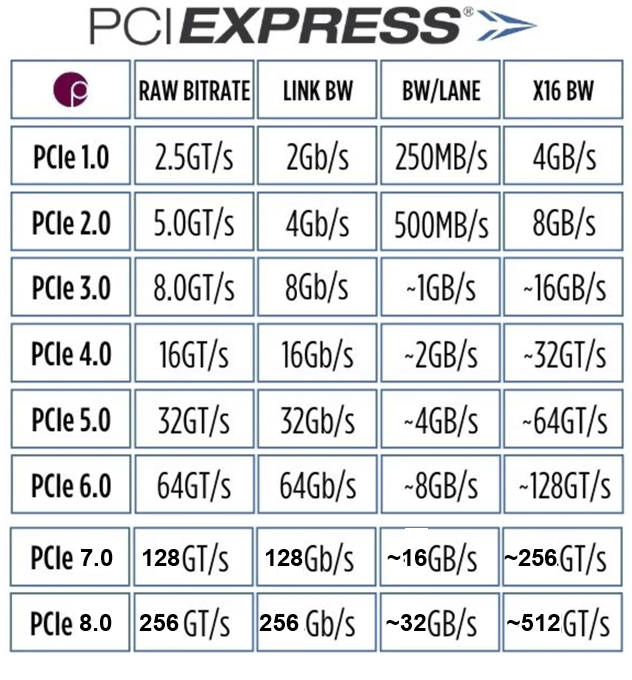

四, PCIe标准带宽

先看一下PCIe不同代的带宽汇总表。

Raw Bit Rate是指每秒发生的传输数据的操作次数,或者说每秒有多少个UI( unit interval)。比如PCIe Gen2,Raw Bit Rate=5.0GT/s,表明它的每秒能完成5,000,000,000个数据的传输,每位数据(Bit)占用的时间宽度=1s/5,000,000,000 =0.2ns=200ps.两个UI为一个数据时钟,因此数据频率=1/(2x200ps)=2.5GHz.测量过PCIe信号的朋友都知道,数据的频率是数据速率的一半。

Link BW(Bandwidth)是指每秒能实际传输到少个bit,PCIe Gen1和PCIe Gen2采用8b/10b编码,实际带宽要乘以8/10,所以PCIe Gen1的实际带宽=2.5GT/s x 8/10 =2Gb/s,而PCIe Gen的实际带宽=5GT/s x 8/10=4Gb/s. PCIe Gen3,PCIe Gen4和PCIe Gen5都采用128b/130b编码,实际带宽损耗可以忽略不计。PCIe Ge6采用Flit 1b/1b编码,实际带宽没有损耗。

BW/Lane是指单个通道lane单方向的实际数据带宽,单位是每秒多少字节(Giga byte per second),因为一个字节byte=8bit,因此BW/Lane= Link BW/ 8.

例如PCIe Gen6,BW/Lane= Link BW/ 8 =64Gb/s /8 =8GB/s

X16 BW是指16个通道lane单方向的实际数据带宽,X16 BW = BW/Lane x 16. 其它不同width的带宽大家可以自己推导。有的文献用双向的吞吐率作为带宽,那么最终的数据要翻倍。

例如PCIe Gen6,X16 BW = BW/Lane x 16 =8GB/s x16 =128GB/s.

五, 总结

PCIe标准每隔几年速率就要翻倍,从2010年Gen3到2017年Gen4之间有7年的停滞一方面是需求没跟上,另一方面是某大厂为了利益而消极怠工。

随着人工智能/机器学习、高速网络、云计算、边缘计算和量子计算等新起,在这些需求的刺激下,PCIe正以风驰电掣的速度发展着。目前network的主流速度是单通道100G,正朝着200G迈进,2028年PCIe的速度将达到恐怖的256Gb/s并首次超越network的速度。

其摧枯拉朽之势不可阻挡,其它的要么顺势一起发展,要么被其超越。

六, 抛砖引玉

PCIe推出了这么多标准,那么具体有哪些PCIe的device呢?

敬请关注下一篇:《PCIe从入门到精通之二:计算机王国中的PCIe设备》

七,参考文献:

需要以下参考文献PCIe标准)的朋友,请关注本微信公众号“硬件工程师宝典”,在对话框内回复“PCIe”,将获取标准下载连接。