DDR5有哪些新功能和特性

0赞0、引言

在本文中,我们将进一步详细介绍与DDR4 SDRAM相比,DDR5在性能、RAS(可靠性、可用性和可服务性)和易于实现方面的改进。

需要以下参考文献(DDR5标准)的朋友,请关注本微信公众号“硬件工程师宝典”,在对话框内回复“DDR5”,将获取标准下载连接。

一、性能

1,Bank总数增加

当memory density增加时,需要扩展Bank的数量以适应增加的memory density。DDR5标准将总Bank的数量增加了一倍,同时保持每个Bank Group内的Bank数量不变。这通过允许同时打开更多pages并增加高pages命中率的统计概率,从而提高了整体系统效率。

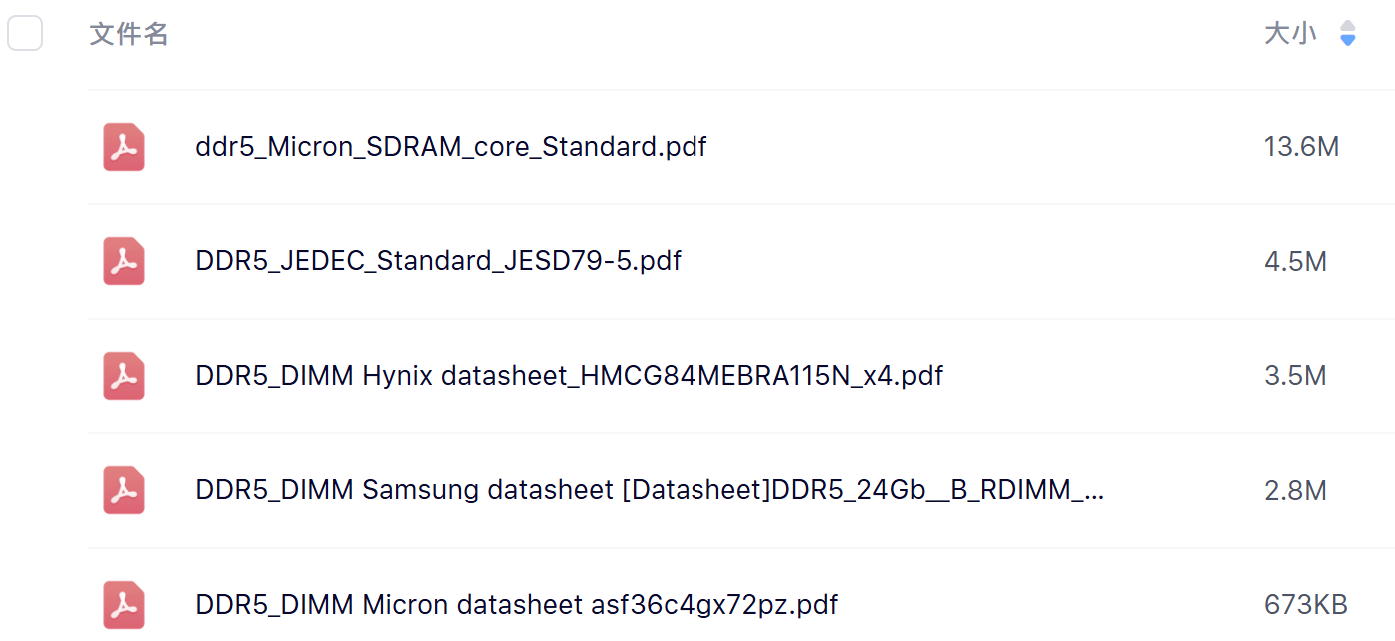

Bank Group间交错时序访问(bank-group-to-bank-group interleaved timing accesses)比特定Bank Group内的Bank间访问(bank-to-bank within the same bank group access)时间更短。这些时序参数具有“Long”时序定义(tCCD_L、tWTR_L、tRRD_L)和“short”时序定义(tCCD_S、tWTR_S、tRRD_S)。Long时序指的是Bank Group内的Bank间访问,而short时序指的是访问不同的Bank Group(如图1所示)。举例来说,tCCD_L几乎可以是tCCD_S的两倍。增加Bank Group通过提高short时序被使用的概率来缓解内部时序限制。

图1:DDR5Bank/Bank Group时序

2,数据Burst Length增加

DDR5 SDRAM的默认Burst Length从DDR4的BL8增加到BL16,提高了command/address和data bus效率。现在,相同的读或写CA总线事务可以在数据总线上提供两倍的数据量,同时限制了在同一Bank内的IO/阵列时序。减少访问给定数据量所需的命令数量,也改善了读写访问的功耗特性。

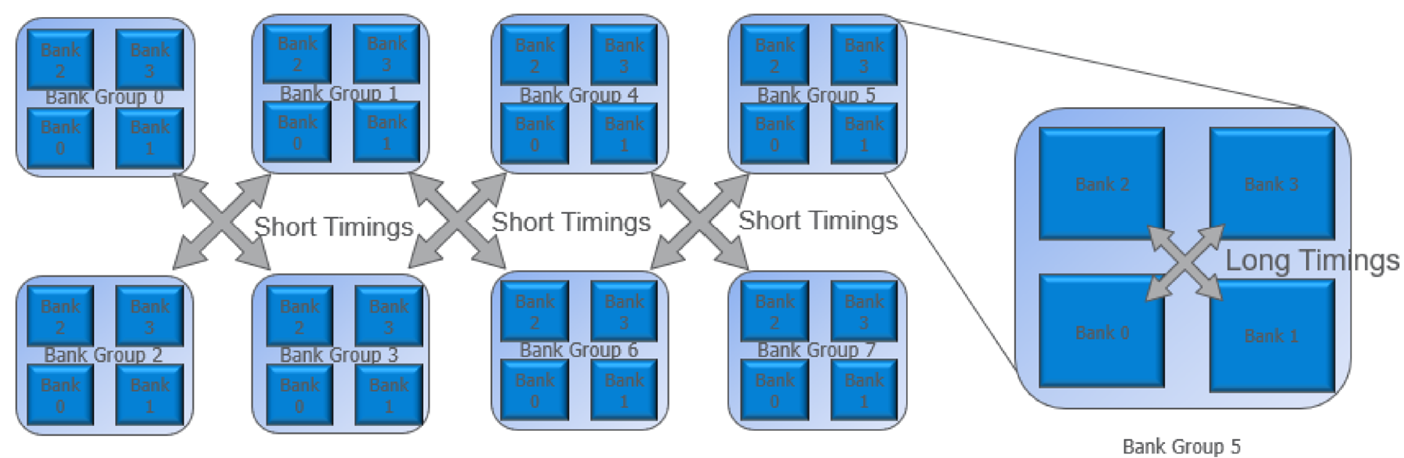

Burst Length的增加还减少了访问相同64B缓存行数据负载所需的IO数量。默认Burst Length的增加使得DDR5 DIMM架构能够实现two sub-channel(如图2所示),这增加了整体通道并发性、灵活性和数量。对于使用128B缓存行数据负载的系统,DDR5专门为x4配置的器件增加了Burst Length 32的选项。这进一步提高了command/address和data bus效率和整体功耗特性。

图2:简化的DDR5 40引脚子通道DIMM示例

3,Refresh Commands

除了DDR5和早期DDR SDRAM产品上可用的标准全Bank Refresh Commands(REFab)外,DDR5还引入了同Bank Refresh Commands(REFsb)。REFsb命令通过command/address bus指定,在发出REFsb命令时,它会针对所有Bank Group中的相同序号的Bank。

SDRAM器件上的Refresh Commands要求目标刷新的Bank在命令发出前处于空闲状态(预充电,无数据活动),并且在Refresh Commands持续期间(时序参数tRFC),这些Bank不能恢复后续的写和读活动。Refresh Commands以平均周期间隔(时序参数tREFI)发出。对于REFab命令,系统必须确保所有Bank在发出命令前处于空闲状态,在“正常”刷新模式下,平均每3.9微秒一次,对于16Gb DDR5 SDRAM器件,持续时间为295纳秒。

REFsb命令的性能优势在于,在发出命令之前,每个Bank Group中只需一个Bank处于空闲状态。其余的12个Bank(对于16Gb、x4/x8器件;图3中的蓝色单元格)在发出REFsb命令时无需处于空闲状态,对未刷新Bank的唯一时序限制是同Bank刷新到激活延迟(时序参数tREFSBRD)。REFsb命令只能在fine granularity refresh(FGR)模式下发出,这意味着每个Bank平均每1.95微秒必须接收一次Refresh Commands。对于16Gb DDR5 SDRAM器件,REFsb的持续时间仅为130纳秒,这也减少了系统访问锁定(tRFCsb)对正在活动的刷新Bank(图3中的红色单元格)的影响。使用REFsb的一个限制是,每个“Same Bank”在发出第二个REFsb命令之前必须接收一个REFsb命令,但REFsb命令可以以任何Bank顺序发出。

图3:DDR5 REFsb Bank映射

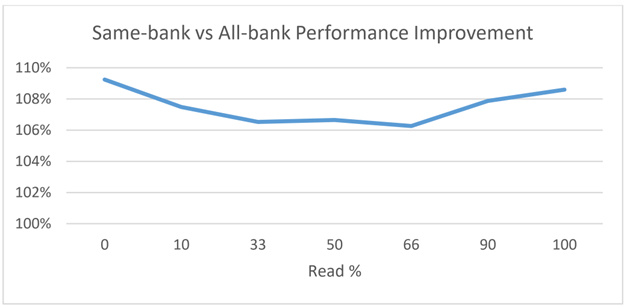

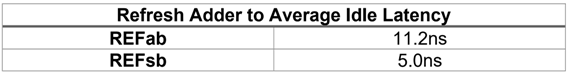

根据read/write命令比率,仿真结果表明,与REFab相比,使用REFsb时系统性能吞吐量可提高6%至9%,如图4所示。此外,REFsb将刷新对平均空闲延迟的影响从11.2纳秒降低到5.0纳秒,如表1所示。计算基于标准排队论,适用于具有随机驱动数据流量的单个Bank。

图4:DDR5系统吞吐量性能提升

表1:DDR5平均空闲延迟增加值

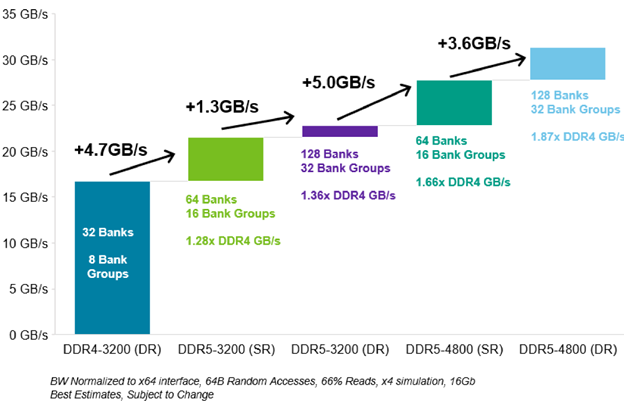

4,性能提升

综合上述特性(2x Bank、2x Bank Group、BL16和Same Bank刷新),并模拟64B随机访问工作负载,与DDR4 3200 MT/s DIMM相比,实现了显著的性能提升,如图5所示。在此场景中,我们假设每个系统有八个channel和1DPC(每channel一个DIMM)。

图5:DDR5按速度/模块等级划分的性能提升

二、可靠性、可用性和可服务性(RAS)

1,On-die ECC

RAS改进,例如On-die ECC,通过在读取命令期间在DDR5器件输出数据之前执行纠错,从而减少了系统纠错负担。DDR5 SDRAM ECC实现为single error correction(SEC),将128个数据位与8个奇偶校验位配对,形成一个136位的码字,在写入命令期间存储在DRAM中。在随后对该地址的读取命令中,将根据136位计算伴随式,纠正可能发生的任何单比特错误。

DDR5设计采用汉明码Hamming codes实现ECC,其中数据位被排列成象限,以与系统级纠错覆盖范围对齐。由于8个奇偶校验位与128个数据位不允许进行双比特检测,汉明码会将一对象限内(象限1和/或2)的两个错误位“别名”到其他象限(象限3或4),或别名到一个“未使用”的数据位。同样,象限3和/或4内的两个错误位将别名到象限1或2,或别名到一个未使用的数据位。这意味着错误仍然会以双比特故障的形式呈现给系统级纠错。

DDR5 SDRAM ECC的另一个附加功能是错误检查和擦洗error check and scrub(ECS)功能。ECS功能是内部数据的读取,以及如果发生错误则将纠正后的数据写回。ECS可以作为由多用途命令Multi-Purpose Command(MPC)启动的手动功能使用,或者DDR5 SDRAM可以在自动模式下运行ECS,DRAM会根据需要调度和执行ECS命令,以在推荐的24小时内完成对阵列中数据位的全面擦洗。在完成一次全阵列扫描后,DDR5 会报告在扫描过程中纠正的错误数量(一旦错误计数超过最低失败阈值),并报告错误数量最多的行,该行也需满足最低阈值。

2,PPR增强功能

封装后修复Post-package repair(PPR)分为两个独立的修复功能:hPPR(硬修复)和sPPR(软修复),它们可能更好地描述为永久修复(hPPR)和临时修复(sPPR)。hPPR在掉电后是非易失性的,而sPPR则不是。

DDR4 SDRAM定义中,每个Bank有多个行北称为关联行(backed-up rows),在sPPR事件发生之前需要进行backup。DDR5对sPPR的一个关键enhancement是减少了在执行sPPR修复之前需要备份的行数。DDR5仅要求在发生sPPR的Bank中有一个目标行。这最大限度地减少了备份和存储大量信息所需的系统时间,通常每行数据大约需要2微秒。

PPR的另一个关键新增功能是跟踪资源可用性的能力。在boot-up时,每个DRAM器件将确定每个Bank中PPR资源的可用性,然后设置一组模式寄存器mode registers(MR54-57)来跟踪此信息。在使用multi-die 3DS堆叠封装的情况下,multi-die 3DS堆叠封装中的每个芯片都将通过相同的模式寄存器进行跟踪。此enhancement为任何已部署系统的内存基础的RAS能力提供了额外的可见性。

三、实现简化

多用途命令Multi-Purpose Command(MPC)

DDR5器件上增加的时钟频率给在initialization和training完成之前执行操作带来了挑战。为了解决这些挑战,开发了多用途命令Multi-Purpose Command(MPC)来执行接口initialization, training和periodic calibration等功能。在早期的DDR SDRAM器件世代中,这些功能要么是单独的命令,要么是模式寄存器设置。

MPC功能在command/address bus包含MPC指令码以及eight operation bits时启动,允许执行多达256种不同的功能。默认的MPC模式设置是多个时钟周期的当CS_n保持低电平时,在此多周期期间命令/地址总线保持不变。这允许通过MPC进入并完成CS training mode。一旦CS_n与CK对齐,MPC可以切换到单周期模式以提高操作效率。

除了执行initialization, training和periodic calibration外,MPC还用于重置DLL、在2N和1N命令时序之间切换、PDA枚举编程和ID选择、设置on-die termination的值以及配置DLL和其他阵列时序。

四、结论

基于DDR5架构DRAM解决方案为行业带来更大的价值。通过增加Bank Group、Burst Length和同Bank refresh等方式实现的显著性能提升,将有助于满足下一代系统的严格要求并降低总拥有成本。DDR5的on-die ECC和PPR增强功能改善了系统RAS。最后,通过使用新的MULTIPURPOSE command功能,内存管理的实现得到了简化。

Note:本文知识来自美光白皮书。

五、参考文献

需要以下参考文献(DDR5标准)的朋友,请关注本微信公众号“硬件工程师宝典”,在对话框内回复“DDR5”,将获取标准下载连接。