PCIe从入门到精通之十一:PCIe设备的配置空间header详解1

0赞0,引言

在上一篇文章《PCIe从入门到精通之十:PCIe配置空间的访问方式详解》中,我们介绍了PCIe配置空间的访问方式。在这一篇文章中我们继续介绍PCIe配置空间前0x3F个寄存器的含义和用途,重点是Type0和Type1相同的部分。

所有PCIe主题的文章都会收录在《深入浅出聊PCIe》合集里,欢迎评阅。

需要下载PCIe学习资料标准的朋友(pdf格式),请关注本微信公众号“硬件工程师宝典”,在对话框内回复“PCIe”,将获取标准下载链接。

一, PCIe配置空间分类

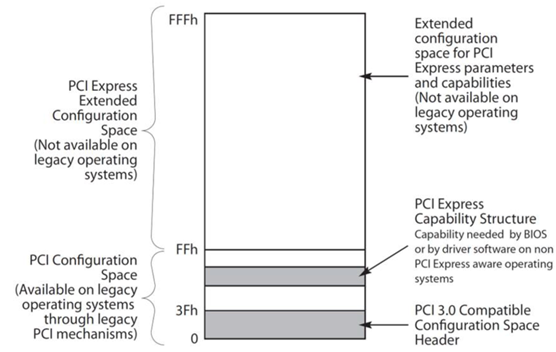

PCIe配置空间分为PCI兼容的配置空间(头部类型PCI header + PCIe Capability Structure)和PCIe扩展配置空间

PCIe架构中的配置空间头部类型PCI header分为Type 0和Type 1,它们的主要区别在于设备在PCIe拓扑中的角色和功能,以及配置空间中包含的寄存器类型。

Type 0 配置空间

用途: Type 0 配置空间用于表示端点设备(Endpoint Device)。端点设备是PCIe拓扑中的叶子节点,通常是实际的硬件功能单元,它们不负责转发或路由PCIe事务,而是直接与主机(Root Complex)或交换机(Switch)通信。

特点: Type 0 配置空间不包含与桥接相关的寄存器,而是包含设备的基本信息,如设备ID、厂商ID、类代码等。

适用设备: 典型的Type 0 设备包括:

显卡(GPU)

网卡(NIC)

存储控制器(如NVMe SSD控制器)

FPGA等直接连接到Root Complex或Switch的设备

Type 1 配置空间

用途: Type 1 配置空间用于表示桥接设备(Bridge Device)。桥接设备用于连接PCIe拓扑中的不同层次,负责转发或路由PCIe事务,从而扩展PCIe拓扑。

特点: Type 1 配置空间包含与桥接相关的寄存器,例如次级总线号(Secondary Bus Number)、下级总线号(Subordinate Bus Number)等,用于管理下游设备的总线号和资源分配。

适用设备: 典型的Type 1 设备包括:

PCIe 交换机(Switch)

根端口(Root Port),连接CPU和PCIe拓扑的根节点

PCIe-to-PCI 桥接器

简单来说(通俗易懂),Type 0 用于实际执行功能的设备(Endpoint,RCiEP, RCEC),他们相当于公司里边的一般员工,俗称牛马;而 Type 1 用于管理和连接这些设备的网络结构(PCI-PCI Bridge),他们是公司里的管理层,俗称领导。

主要区别总结

特性 | Type 0(端点设备) | Type 1(桥接设备) |

设备角色 | 端点设备(叶子节点) | 桥接设备(中间节点) |

事务转发 | 不转发事务 | 转发或路由PCIe事务 |

配置空间 | 不包含桥接相关寄存器 | 包含桥接相关寄存器(如总线号) |

典型设备 | GPU、网卡、存储控制器、FPGA等 | PCIe Switch、Root Port、PCIe-to-PCI 桥接器等 |

在拓扑中 | 实际的硬件功能单元,位于拓扑的末端 | 连接不同层次,扩展拓扑结构 |

二, PCIe Type0和Type1配置空间的区别

在PCI兼容的配置空间里,前0h~3Fh存放的是PCI header(device基本信息),后面的40h~FFh存放的是PCIe Capability Structure(device都有哪些本领)。其中,header: 0h~3Fh里,Type0与Type1两者部分相同,有部分不同;Capability Register:40h~FFh里,Type0与Type1两者相同;

在扩展配置空间里(Byte 100h~FFFh),全部存放的是PCIe Extended Parameters and Capability Structure。Capability Register: Byte100h~FFFh里,两者相同。

总结如下:

配置空间类型 | 配置空间offset | Type0 与 Type1 |

PCI兼容的配置空间 | header: 0h~3Fh | 两者部分相同 |

Capability Register:40h~FFh | 两者相同 | |

PCIe扩展配置空间 | Capability Register: Byte 100h~FFFh | 两者相同 |

三,PCI兼容的配置空间里Type0和Type1相同的部分

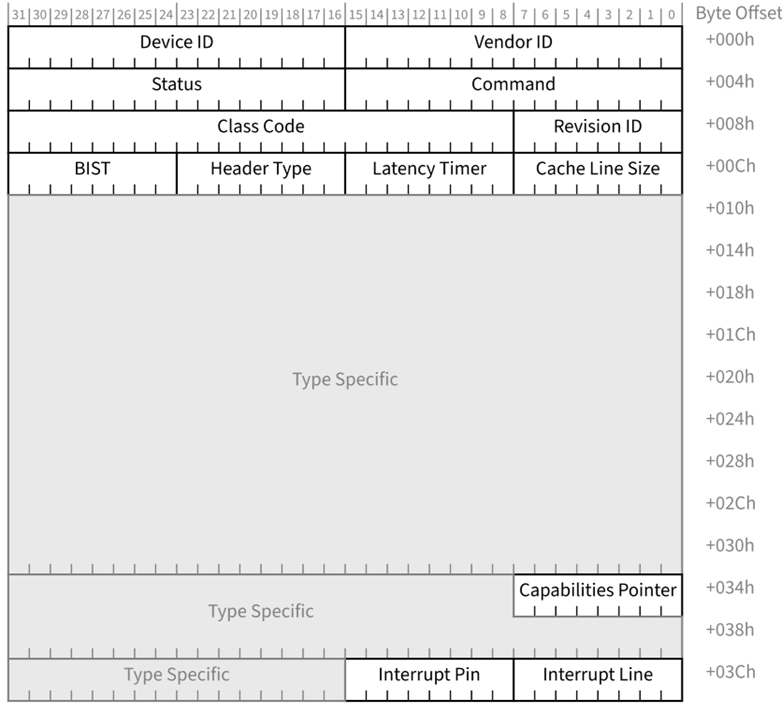

共同的配置空间头部字段 (前16字节),以下是PCIe Type 0和Type 1配置空间中共同的详细字段解析:

这部分是所有PCIe设备配置空间头部的标准组成部分,用于设备识别、状态报告和基本控制。

1) Vendor ID (00h-01h)

大小: 16位

描述: 标识设备的制造商。由PCI SIG(Special Interest Group)分配。

用途: 操作系统和驱动程序通过此ID识别设备的制造商。

2) Device ID (02h-03h)

大小: 16位

描述: 标识制造商生产的特定设备。由设备制造商分配。

用途: 与Vendor ID结合,唯一标识一个特定的设备型号。

3) Command (04h-05h)

大小: 16位

描述: 控制设备的各种功能。

重要位:

Bit 0 (I/O Space Enable): 控制设备是否响应I/O空间访问。

Bit 1 (Memory Space Enable): 控制设备是否响应内存空间访问。

Bit 2 (Bus Master Enable): 控制设备是否能够作为总线主控发起DMA(直接内存访问)请求。

Bit 4 (Memory Write and Invalidate Enable): 允许设备在写入内存时使用内存写入并失效(MWI)事务。

Bit 6 (Parity Error Response): 控制设备是否在检测到奇偶校验错误时生成Serr#信号。

Bit 10 (Interrupt Disable): 禁用设备中断。

用途: 驱动程序通过设置这些位来启用或禁用设备的特定功能。

4) Status (06h-07h)

大小: 16位

描述: 报告设备的当前状态和错误信息。

重要位:

Bit 3 (Interrupt Status): 指示设备是否有待处理的中断。

Bit 4 (Capabilities List): 如果此位为1,表示在偏移量34h处有一个指向能力列表的指针。这是PCIe设备的关键特性,因为它指向PCIe能力结构和其他扩展能力。

Bit 5 (66 MHz Capable): 报告设备是否支持66 MHz操作(PCIe中通常不相关)。

Bit 8 (Master Parity Error): 指示设备在发起总线主控事务时检测到奇偶校验错误。

Bit 9 (DEVSEL Timing): 报告设备DEVSEL#信号的定时(PCIe中不相关)。

Bit 11 (Signaled Target Abort): 指示设备作为目标时终止了事务。

Bit 12 (Received Target Abort): 指示设备作为发起者时接收到目标终止。

Bit 13 (Received Master Abort): 指示设备作为发起者时接收到主控终止。

Bit 14 (Signaled System Error): 指示设备发出了系统错误(SERR#)。

Bit 15 (Detected Parity Error): 指示设备检测到奇偶校验错误。

用途: 操作系统和驱动程序通过此寄存器获取设备的状态和错误信息。

5) Revision ID (08h)

大小: 8位

描述: 标识设备的硬件修订版本。

用途: 驱动程序可以使用此ID来识别特定的硬件版本,并根据需要应用不同的兼容性或性能优化。

6) Class Code (09h-0Bh)

大小: 24位(3字节)

描述: 描述设备的通用功能类型。分为三部分:

Base Class (0Bh): 8位,定义设备的主要功能类别(例如,0x01表示存储控制器,0x02表示网络控制器,0x03表示显示控制器,0x06表示桥接设备)。

Sub-Class (0Ah): 8位,定义设备在Base Class下的具体子类别(例如,对于Base Class 0x06,Sub-Class 0x04表示PCI-to-PCI桥)。

Programming Interface (09h): 8位,定义设备特定的编程接口(例如,对于以太网控制器,可以指示支持的MII接口)。

用途: 操作系统和驱动程序通过Class Code来识别设备的类型,并加载相应的通用驱动程序或执行特定的配置。

7) Cache Line Size (0Ch)

大小: 8位

描述: 指示系统高速缓存行的大小,以32位字为单位。

用途: 供设备在执行DMA操作时参考,以优化数据传输。在PCIe中,此字段通常设置为0,因为PCIe事务是基于包的,而不是基于缓存行的。

8) Latency Timer (0Dh)

大小: 8位

描述: 在旧的PCI总线中,用于控制设备作为总线主控时可以占用总线的时间片。

用途: 在PCIe中,此字段通常设置为0,因为它不再用于控制总线仲裁。PCIe使用更复杂的流量控制和服务质量(QoS)机制。

9) Header Type (0Eh)

大小: 8位

描述: 标识配置空间的头部布局,以及设备是否为多功能设备。

重要位:

Bit 7 (Multi-function Device): 如果此位为1,表示设备是一个多功能设备(例如,一个网卡芯片上集成了多个以太网端口)。

Bits 6:0 (Header Layout):

00h: 表示Type 0头部,用于端点设备。

01h: 表示Type 1头部,用于桥接设备(如PCIe Switch或Root Port)。

用途: 操作系统通过此字段判断配置空间的其余部分是按照Type 0还是Type 1的格式进行解析。

10) BIST (Built-In Self Test) (0Fh)

大小: 8位

描述: 用于控制和报告设备的内置自检功能。

用途: 允许系统在启动时对设备进行自检。

11) 共同的扩展能力指针

除了上述前16字节的共同头部,还有一个非常重要的共同字段,它位于标准配置空间的第52字节(偏移量34h):

Capabilities Pointer (34h)

大小: 8位

描述: 如果Status寄存器中的"Capabilities List"位(Bit 4)被设置,则此寄存器包含一个指向设备配置空间中第一个能力结构(Capability Structure)的偏移量。

用途: PCIe设备通过能力列表来报告其支持的各种高级功能,例如PCIe能力、电源管理、MSI/MSI-X中断、热插拔等。操作系统和驱动程序通过遍历这个列表来发现和配置这些高级功能。这个指针是PCIe设备能够支持其复杂功能的基础。

12) 总结

尽管Type 0和Type 1设备在配置空间中后续的字段布局(例如Base Address Registers、总线号等)有所不同,但它们都共享上述前16字节的头部信息以及Capabilities Pointer。这些共同的字段确保了系统能够对所有PCIe设备进行基本的识别、状态查询和功能使能,为后续针对特定设备类型(端点或桥接)的详细配置奠定了基础。

四,抛砖引玉

在这一章中我们介绍了前0x3F个寄存器以及Type0和Type1的相同部分,那么前0x3F个header寄存器中Type0和Type1不同部分有哪些?它们有什么含义?下一章的重点是Type0和Type1不同的部分。

敬请关注下一篇:《PCIe从入门到精通之十二:PCIe设备的配置空间header详解2》

五,参考文献:

需要以下参考文献(PCIe标准)的朋友,请关注本微信公众号“硬件工程师宝典”,在对话框内回复“PCIe”,将获取标准下载链接。

百度网盘分享的文件