I2C从入门到精通之三:I2C信号的特性和操作

0赞0,引言

在上一篇文章我们讲解了《I2C从入门到精通之二:I2C设备的硬件架构》,今天我们继续接着介绍I2C信号的特性和操作。

所有I2C主题的文章都会收录在《深入浅出聊I2C》合集里,欢迎评阅。通过这个专集的阅读,你将成为I2C专家。

百度网盘分享的文件

上如是I2C学习资料和标准(pdf格式),需要下载的朋友,请关注本微信公众号“硬件工程师宝典”,在对话框内回复“I2C”,将获取标准下载链接。其中“I2C_Spec_Rev7_2021_UM10204.pdf”这份文件是最新的I2C specification, 希望大家重点阅读。

一、 I2C设备输入缓冲器特点

1.1 用于双向通信的开漏电路

开漏是指一种输出类型,它可以将总线拉低到某个电压(在大多数情况下是接地),或者“释放”总线并让它被上拉电阻拉高。在主设备或从设备释放总线的情况下,信号线上的上拉电阻(RPU)负责将总线电压拉高到power rail。由于没有设备可以强制将信号线路拉到高电平,这意味着总线永远不会遇到通信问题,即一个设备可能尝试传输高电平,而另一个设备传输低电平,导致短路(power rail到地)。I2C要求,在多主设备环境中,如果一个主设备传输高电平,但发现线路为低电平(另一个设备正在将其拉低),则停止通信,因为另一个设备正在使用总线。推挽式接口不允许这种模式,这是I2C的一个优点。

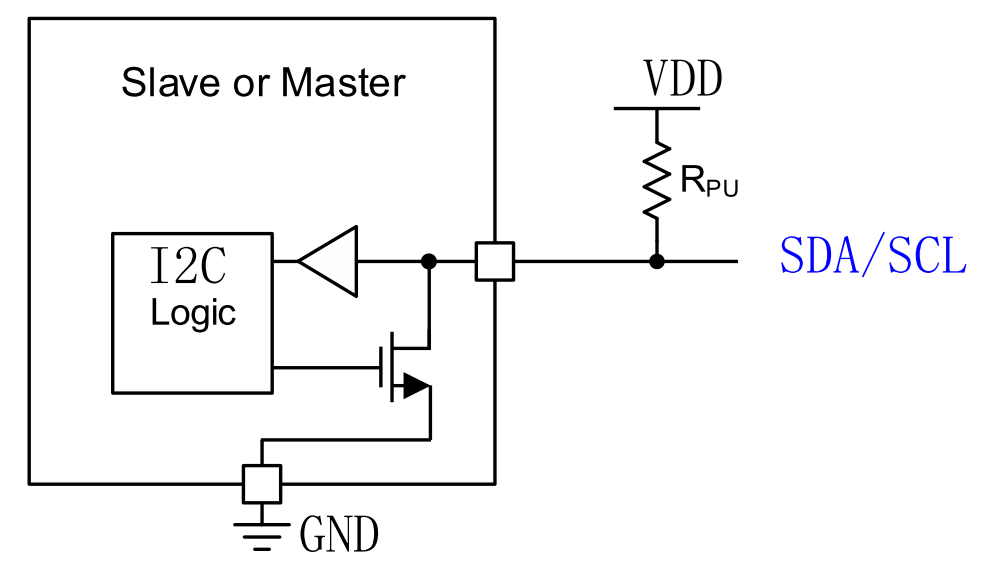

图2. SDA/SCL线路基本内部结构

图2显示了SDA/SCL线上从设备或主设备内部结构的简化视图,包括一个用于读取输入数据的缓冲器和一个用于传输数据的下拉FET。设备只能将总线信号线拉低(提供对地的短路)或释放总线信号线(对地高阻抗)并允许上拉电阻拉到高电压。在处理I2C设备时,这是一个重要的概念,因为没有设备可以保持总线为高电平。正是这个特性允许双向通信发生。

要设置 SDA 或 SCL 线的电压水平,需将 NMOS 设为开启或关闭状态。

1.2 开漏拉低

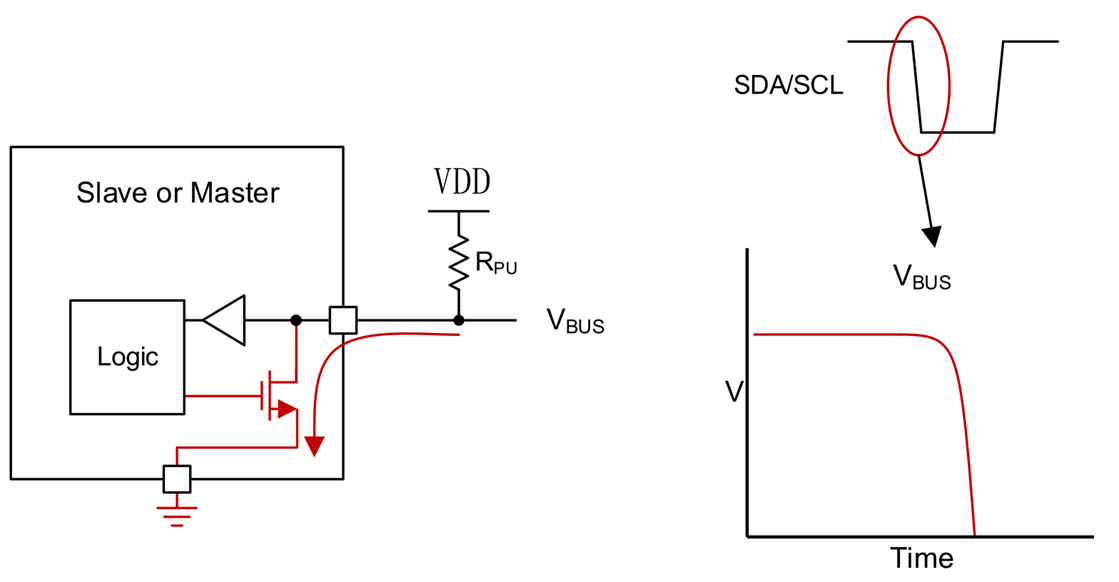

如前一节所述,开漏设置只能将总线拉低,或“释放”它并让上来电阻将其拉高。当 NMOS 开启时,该设备会通过电阻将电流拉至地端。这会使开漏输出线电平降低。通常,I2C 从高电平到低电平的转换是一个快速转换,因为 NMOS 会向下拉低 SDA 或 SCL 线。转换的速度取决于 NMOS 的驱动强度以及 SDA 或 SCL 线上的任何总线电容。

图3显示了将总线拉低时的电流流向。想要传输低电平的逻辑将激活下拉FET,这将提供对地的短路,从而将线路拉低。

图3. 使用开漏接口将总线拉低

1.3 开漏释放总线

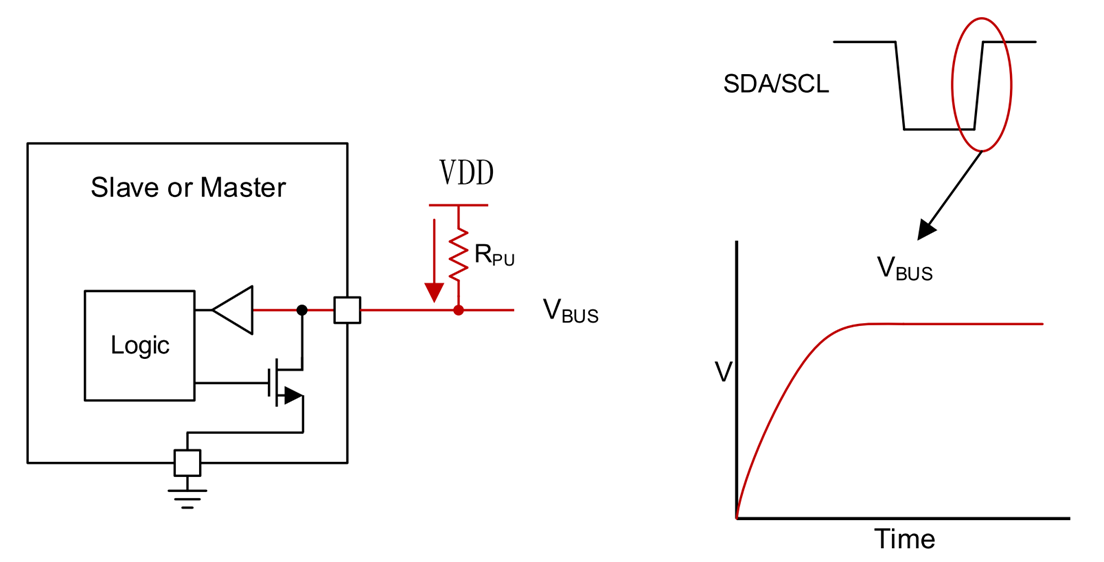

当从设备或主设备希望传输逻辑高电平时,它只能通过关闭下拉FET来释放总线。这会使总线浮空,上拉电阻会将电压拉高到power rail,这将被解释为高电平。当 NMOS 关闭时,该设备停止拉电流,并且上拉电阻将 SDA 或 SCL 线拉至 VDD。图4 展示了 NMOS 关闭时的开漏输出线。上拉电阻将该线拉高。开漏输出线的转换速度较慢,因为该线是与总线电容对抗而被拉高的,并且不是被主动驱动的。

图4显示了电流通过上拉电阻的流向,上拉电阻将总线拉高。

图4. 使用开漏接口释放总线

二、 I2C通用操作

I2C总线是一种标准的双向接口,使用一个控制器(称为主设备)与从设备进行通信。从设备不能主动传输数据,除非它已被主设备寻址。I2C总线上的每个设备都有一个特定的设备地址,以区分同一I2C总线上的其他设备。许多从设备在启动时需要配置以设置设备的行为。这通常在主设备访问从设备的内部寄存器映射时完成,这些寄存器映射具有唯一的寄存器地址。一个设备可以有一个或多个存储、写入或读取数据的寄存器。

物理I2C接口由串行时钟(SCL)和串行数据(SDA)线组成。SDA和SCL线都必须通过上拉电阻连接到VCC。上拉电阻的大小由I2C线上的电容决定(有关I2C上拉电阻计算,会在后面章节中讲解)。数据传输只能在总线空闲时启动。如果SDA和SCL线在STOP条件后都为高电平,则认为总线空闲。

主设备访问从设备的通用过程如下:

1. 假设主设备想要向从设备发送数据:

• 主发送器发送一个START条件并寻址从接收器

• 主发送器向从接收器发送数据

• 主发送器以STOP条件终止传输

2. 如果主设备想要从从设备接收/读取数据:

• 主接收器发送一个START条件并寻址从发送器

• 主接收器向从发送器发送请求读取的寄存器

• 主接收器从从发送器接收数据

• 主接收器以STOP条件终止传输

3 START和STOP条件

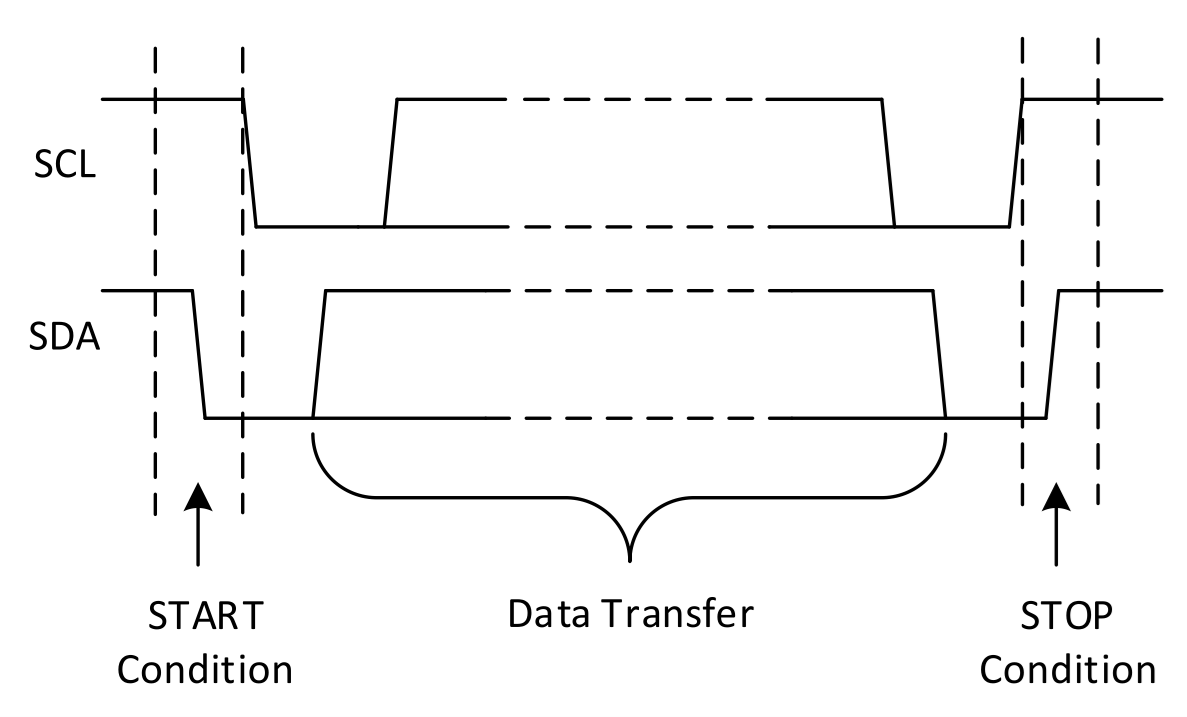

与该设备的I2C通信由主设备发送START条件启动,并由主设备发送STOP条件终止。当SCL为高电平时,SDA线上的高到低转换定义为START条件。当SCL为高电平时,SDA线上的低到高转换定义为STOP条件。

图5. START和STOP条件示例

4 重复START条件

重复START条件类似于START条件,用于替代连续的STOP然后START条件。它看起来与START条件相同,但与START条件不同,因为它发生在STOP条件之前(当总线不空闲时)。这对于主设备希望开始新的通信,但又不希望通过STOP条件让总线空闲,从而可能在多主设备环境中失去对总线的控制时非常有用。

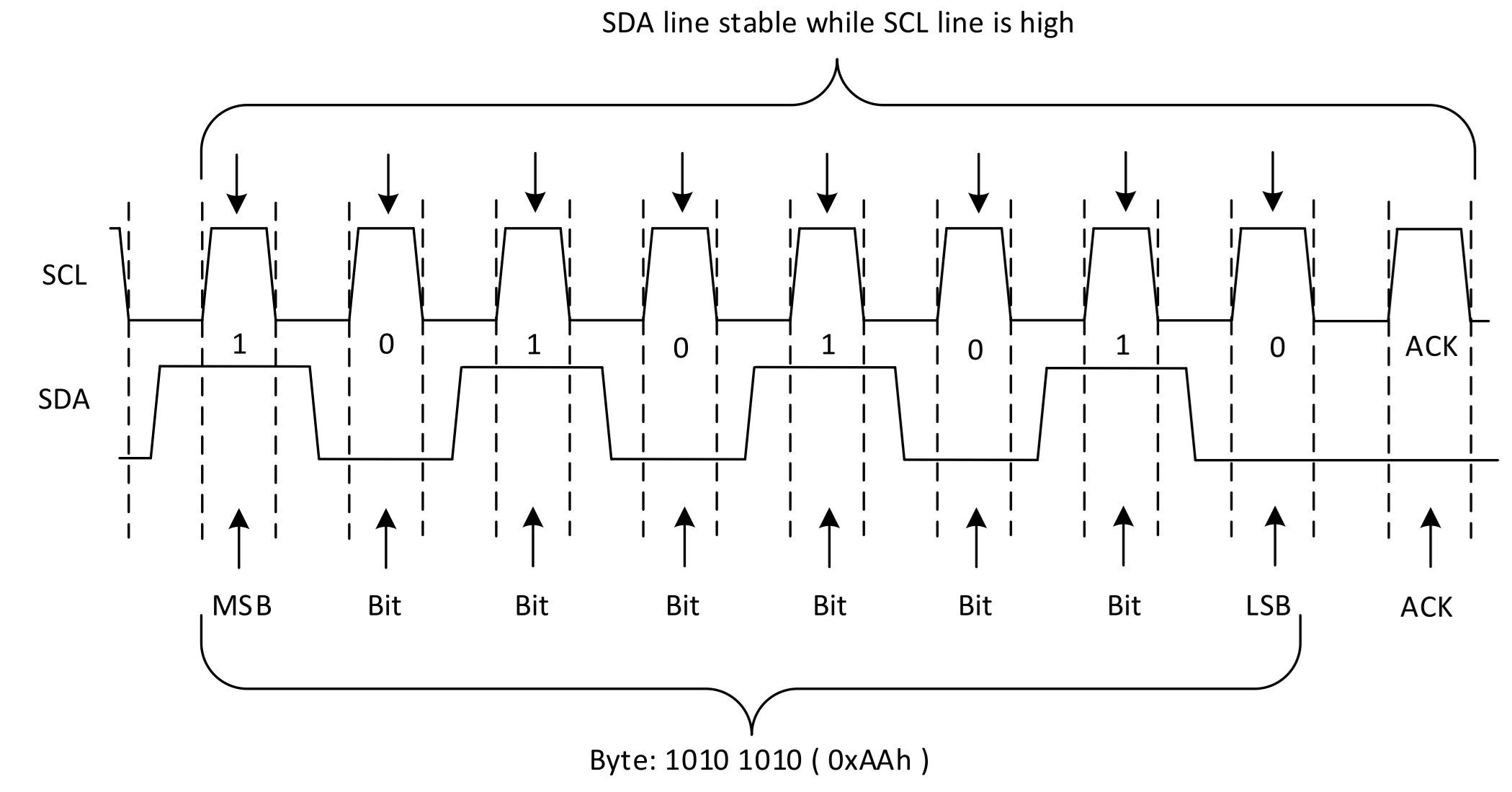

5 数据有效性和字节格式

在SCL的每个时钟脉冲期间传输一个数据位。一个字节由SDA线上的八位组成。一个字节可以是设备地址、寄存器地址,或者写入或读取从设备的数据。数据以最高有效位(MSB)优先传输。在START和STOP条件之间,主设备可以向从设备传输任意数量的数据字节。当SCL为高电平时,SDA线上的数据必须保持稳定,因为当SCL为高电平时数据线上的变化被解释为控制命令(START或STOP)。

图6. 单字节数据传输示例

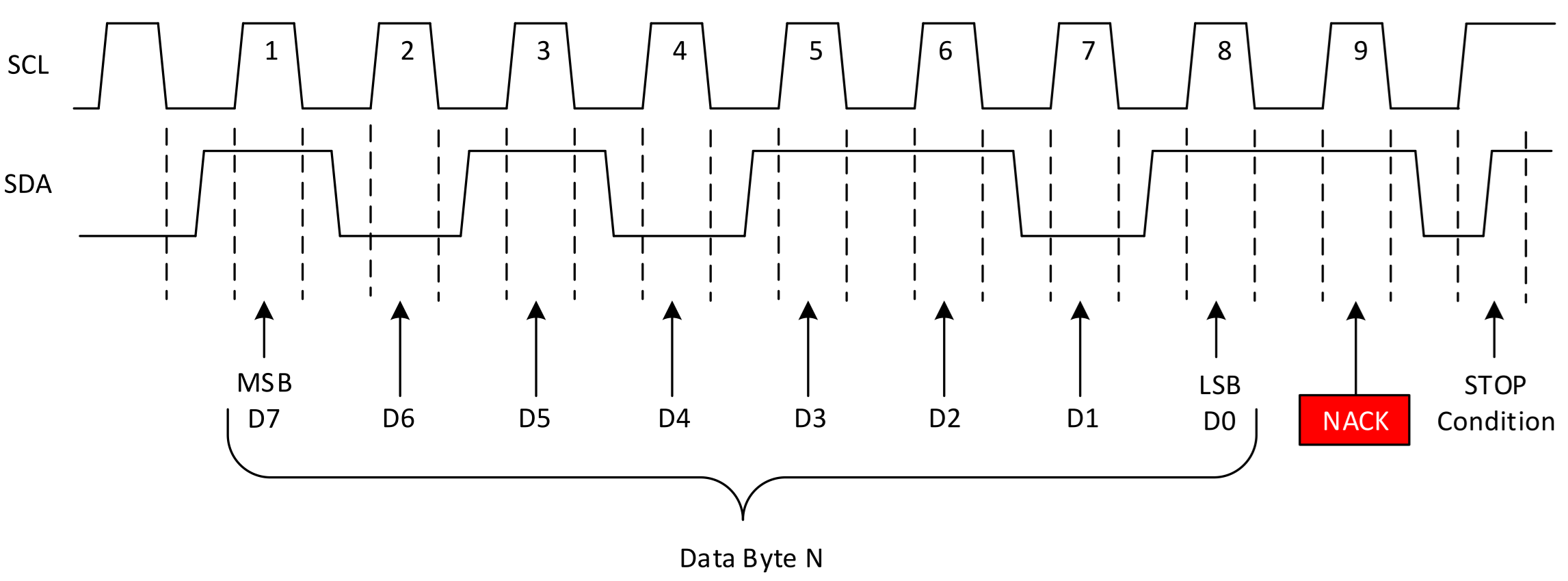

6 应答 (ACK) 和非应答 (NACK)

每个数据字节(包括地址字节)之后都跟着接收器发出的一个ACK位。ACK位允许接收器向发送器通信,表明字节已成功接收,并且可以发送另一个字节。

在接收器发送ACK之前,发送器必须释放SDA线。为了发送ACK位,接收器应在ACK/NACK相关时钟周期(周期9)的低电平阶段将SDA线拉低,以便在ACK/NACK相关时钟周期的高电平阶段SDA线保持稳定低电平。必须考虑建立和保持时间。

当SDA线在ACK/NACK相关时钟周期内保持高电平时,这被解释为NACK。导致生成NACK的几种情况:

1)接收器无法接收或传输,因为它正在执行某些实时功能,尚未准备好与主设备开始通信。

2)在传输过程中,接收器收到它不理解的数据或命令。

3)在传输过程中,接收器无法再接收更多数据字节。

4)主接收器已完成数据读取,并通过NACK向从设备指示。

图7. NACK波形示例

三, 抛砖引玉

这种简洁的硬件架构和连接方式使得I2C总线在各种嵌入式应用中非常受欢迎,因为它减少了引脚数量、布线复杂性,并降低了系统成本。

在接下来的文章中,我们将深入介绍I2C从设备的地址address。

敬请关注下一篇:《I2C从入门到精通之四:I2C从设备的地址address》

七,参考文献:

需要以下参考文献(I2C标准)的朋友,请关注本微信公众号“硬件工程师宝典”,在对话框内回复“I2C”,将获取标准下载连接。其中“I2C_Spec_Rev7_2021_UM10204.pdf”这份文件是最新的I2C specification, 希望大家重点阅读。

百度网盘分享的文件