RDMA设计8:状态管理单元设计

0赞

发表于 12/2/2025 8:36:12 AM

阅读(93)

本文主要交流设计思路,在本博客已给出相关博文一百多篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。若有NVME或RDMA 产品及项目需求,请看B站视频后联系。

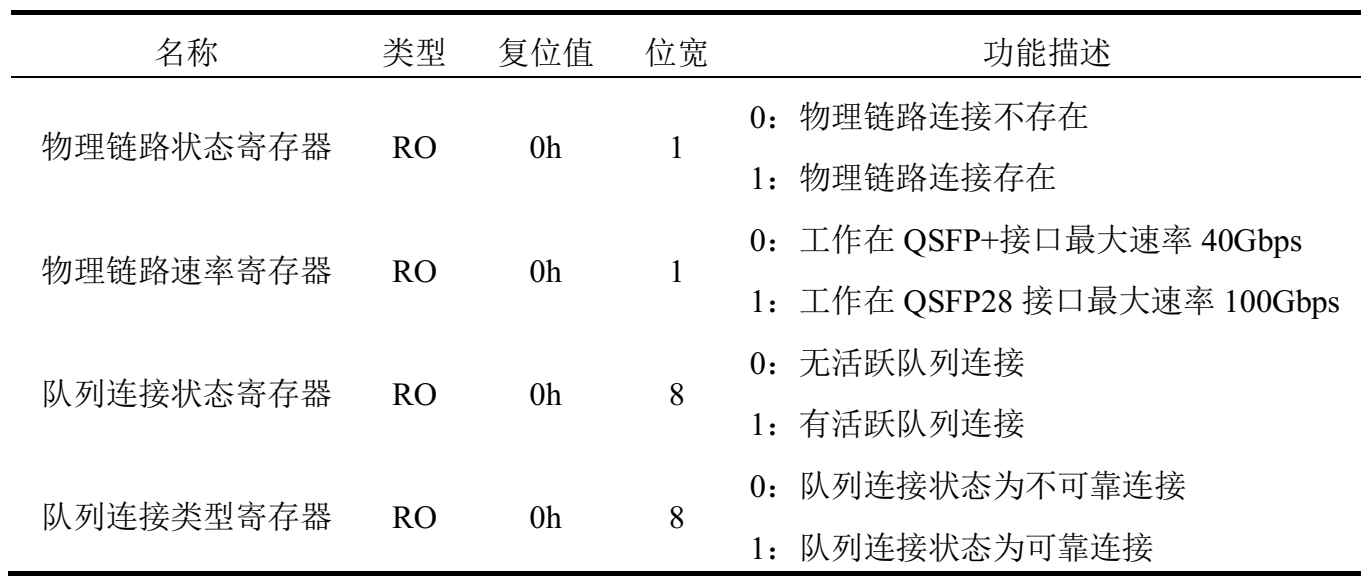

状态管理单元负责读取系统工作状态,包括物理链路连接状态和队列连接状态,并反馈给上位机。状态管理寄存器组定义如表1 所示。

表1 状态管理寄存器组定义

其中,物理链路状态寄存器反映了当前系统的物理层连接状态,即光缆是否连接妥当;物理链路速率寄存器表示当前系统物理层握手速率;队列连接状态及队列连接类型寄存器反映与主机的队列连接状态及类型,其位宽与本系统建立连接的主机数量,最大位宽为 8。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

https://www.bilibili.com/video/BV1mPV5eCE8z/?spm_id_from=333.337.search-card.all.click&vd_source=c355545d27a44fe96188b7caefeda6e7