边沿检测--edge_test

0赞观《从零开始走进FPGA世界》V2.0 之边沿检测

边沿检测的目的:在上升沿,下降沿到来的时候,时序能够及时准确的检测到

/*

Module name edge test

Target Device EP2C8Q208C8

*/

module edge_test

(

input clk, // global clock

input rst_n, // global reset

input signal, //

output pos_edge, //

output neg_edge //

);

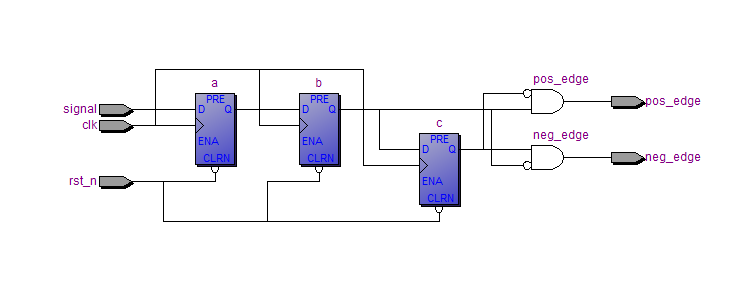

//一般为了防止触发信号的波动,会加上几级触发器,消除抖动,使得信号更稳定

//使用触发器对信号打慢两排,使得触发信号稳定后再进行相关处理,再来检测上升沿,下降沿

reg a,b,c;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

a <= 1'b0;

b <= 1'b0;

c <= 1'b0;

end

else

begin

a <= signal;

b <= a;

c <= b;

end

end

assign pos_edge = b & ~c;

assign neg_edge = ~b & c;

endmodule

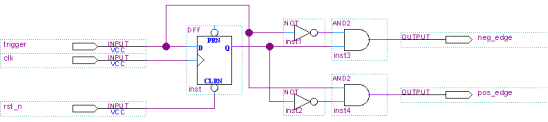

t0时刻为高电平,t1时刻为低电平,经与门输出neg_edge为高,表示检测到下降沿

t0时刻为低电平,t1时刻为高电平,经与门输出pos_edge为高,表示检测到上升沿