在Vivado下进行功耗估计和优化——高亚军

0赞作者:高亚军

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

功耗估计

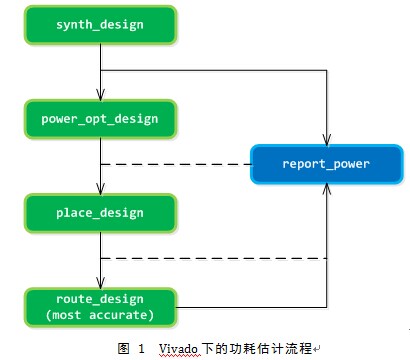

在Vivado下,从综合后的设计到布局布线后的设计,其间产生的任何DCP文件都可用于功耗估计,如图 1所示。打开综合后的设计或布局布线后的设计,既可以在图形界面模式下,选择Report Power,也可以直接用Tcl命令report_power获取功耗估计结果。其中,利用布局布线后的设计可获得更为精确的功耗估计结果。

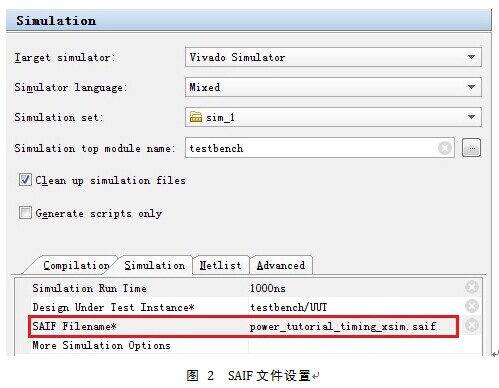

在Vivado下,有两种功耗估计模式。一种是向量模式,需要提供SAIF(Switching Activity Interchange Format)或VCD文件;一种是非向量模式,只需要提供简单的参数即可,但估计结果不够准确。SAIF文件通过仿真生成,因此需要在Simulation Settings中进行设置,如图 2所示。这里的仿真只能是综合后的功能/时序仿真或者布局布线后的功能/时序仿真,这是由图 1的流程决定的。Xilinx建议在向量模式下选择SAIF文件,因其估计速度要比VCD快。

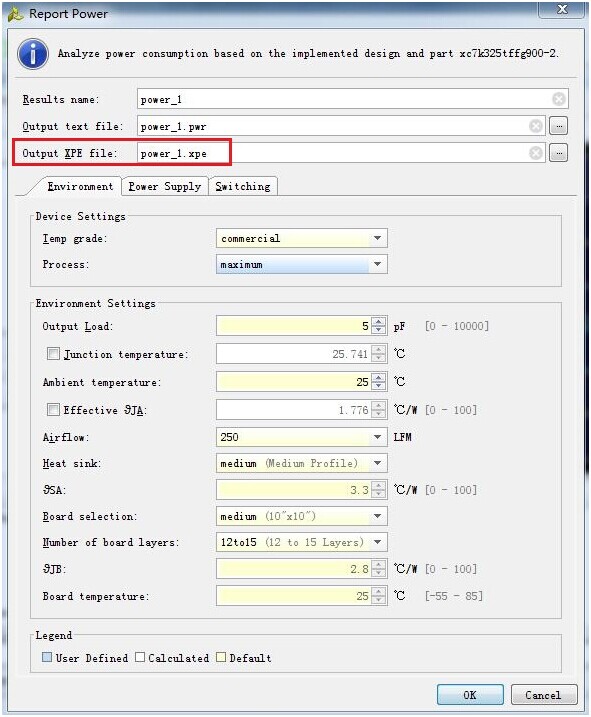

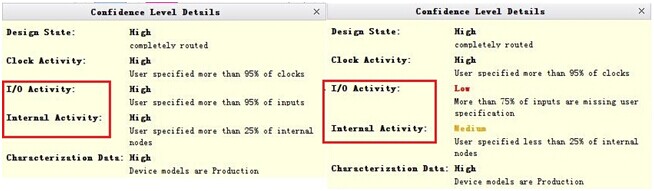

选择Report Power之后,弹出图 3所示的界面,填入相应的参数,如果是向量模式,在Switching窗口中选择相应的SAIF文件,如图 4所示。可以看到Report Power能够生成XPE功耗估计所需文件。功耗估计的结果如图 5所示,可以看到采用向量模式结果的confidence level为high,非向量模式为low。之所以有这样的结果,是因为SAIF文件提供了内部信号和对外输入输出端口信号的翻转率,如图 6中的I/O Activity和Internal Activity所示。

图 3 Report Power界面

图 4 Report Power中的SAIF文件接口

图 5 图5 功耗估计结果

图 5 图5 功耗估计结果

图 6 confidence level high和low的原因

功耗优化

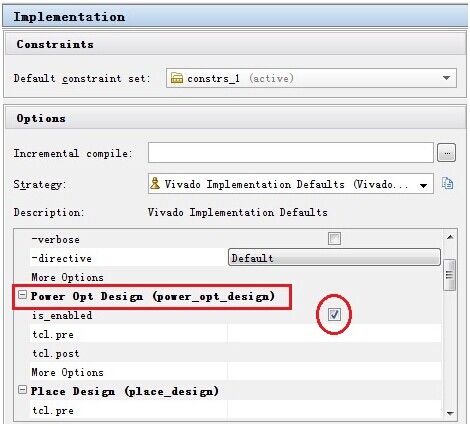

在Implementation阶段,有专门针对功耗优化的流程,如图 7所示。有布局之前的power_opt_design,也有布局之后的power_opt_design。相比而言,布局之前的power_opt_design对功耗的优化更彻底、更全面。

图 7 针对功耗优化的流程

选中图 7中的is_enabled,并运行implementation,结束之后打开布局布线后的设计,在菜单中选择Tool>Report>Report Power Optimization,或者用Tcl命令report_power_opt,可查看power_opt_design对功耗的优化报告,如图 8所示。可以看到,Vivado通过对BRAM添加使能信号(图中的TOOL GATED)控制信号的翻转率,达到降低功耗的目的。

图 8 功耗优化报告

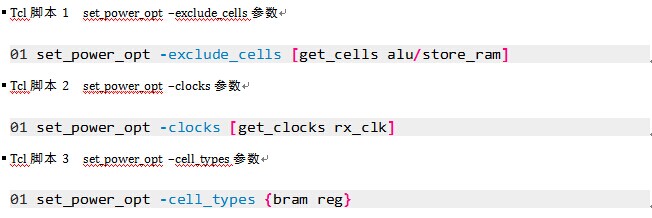

功耗优化的目的是最大限度地降低FPGA功耗同时最小限度地避免其对时序的影响。但有时会出现功耗优化之后(运行power_opt_design)时序恶化甚至无法收敛的情况,此时可通过Tcl命令set_power_opt来控制功耗优化的对象。例如,对alu模块中的store_ram不进行优化,可通过Tcl脚本 1实现;若只对某时钟域进行优化,可通过Tcl脚本 2实现;若只对某类型的cell优化,可通过Tcl脚本 3实现。

综上所述,为了获得较为准确的功耗估计结果,应尽可能地提供SAIF文件,同时对设计中的所有时钟给出合理地约束,此外,对于扇出较大的控制信号也要给出其翻转率。功耗优化在设计之初就应考虑,设计中应遵循好的RTL代码风格,例如尽量避免对触发器和BRAM使用异步复位或置位,适时地选择布局前的power_opt_design和布局后的power_opt_design,并根据功耗优化对设计时序的影响,通过set_power_opt管理优化对象。

参考文献

[1] Xilinx. Ug997 (V2014.2) Power Analysis and Optimization

[1] Xilinx. Ug835 (V2014.2) Vivado Design Suite Tcl Command Reference Guide