【再说FPGA】设计和仿真6.25G速率下的ALTERA器件StratixII GX

0赞设计和仿真6.25G速率下的ALTERA器件StratixII GX

王敏志

概述

点对点的高速设计可以利用ALTERA的GXB之Basic模式来实现,ALTERA给出了这种模式下6.25G速率下参考实例。本文基于Stratix II GX器件介绍GXB设计和仿真,特别需要提到的是笔者一直在使用ArriaGX,这个系列和Stratix II GX一样最高可支持32 bits位宽,只是笔者一直在使用16-bit模式,而此模式无法使能Byte Ordering模块。另外,这个例子的亮点是仿真了Byte Ordering模块。笔者的产品应用中并没有使用这个模块,所以字节对齐都是通过手动完成,通过这个例子GXB似乎可以自动完成字节对齐,仿真是没有问题,还是需要进一步上板子进行验证。本文只关心仿真,后续的上板验证结果另行报告。

注:ModelSim版本为ModelSim SE PLUS 6.5a。

实例简介

例子中的GXB包括发送和接收各一个通道,一起例化。收发通道的主要配置参数满足下列条件:

l 156.25MHz的32-bit并行数据,双工通道

l 使能8B/10B编解码

l Word alignment的控制码是K18.5

l Byte ordering控制码是K27.7

设计包含一个数据发生模块(data generator),重复产生32’hBCBCBCBC控制符(K28.5)后跟一个32’hFBFBFBFB控制符和32’h00000000,32’h01010101,32’h02020202... … 32’hFFFFFFFF数据。

另外,必须包含一个复位和上电控制逻辑模块,用于确保Transceiver得到正确的复位流程。

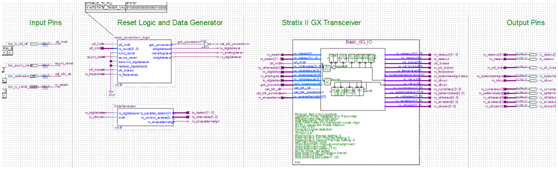

图1:工程top level

GXB参数设置

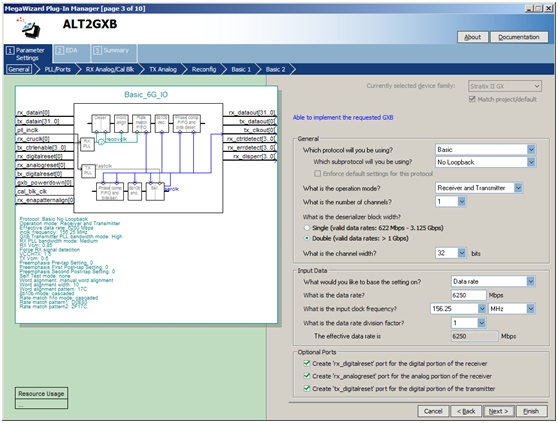

本节详细介绍GXB的参数设置,以下是step by step介绍每一页参数设置界面。图2是通用参数设置界面,选择Basic协议,双工模式,所以操作模式设置为“Receiver and Transmitter”,通道数选择1,位宽32-bit,输入时钟156.25MHz,并设置速率6250Mbps。

图2:Transceiver通用参数设置界面

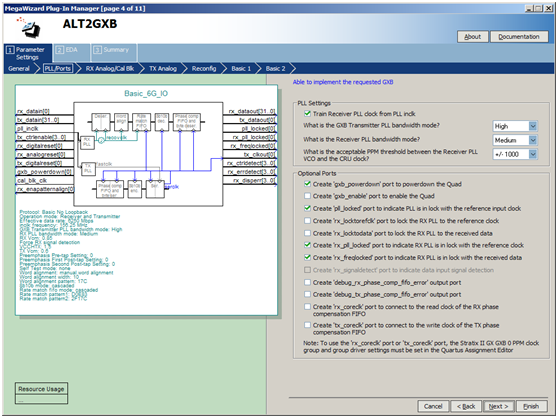

图3:RX和TX PLL的参数配置

图3是收发器的PLL配置界面,图中“train the receiver PLL”被使能,说明RX和TX使用同一个输入时钟,否则TX和RX分别有独立的时钟输入端口。另外,最好使能接收的rx_pll_locked和rx_freqlocked端口,调试的时候会用到。

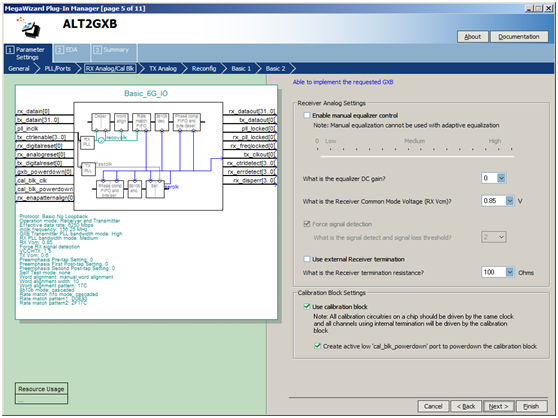

图4:接收端模拟和校正模块配置

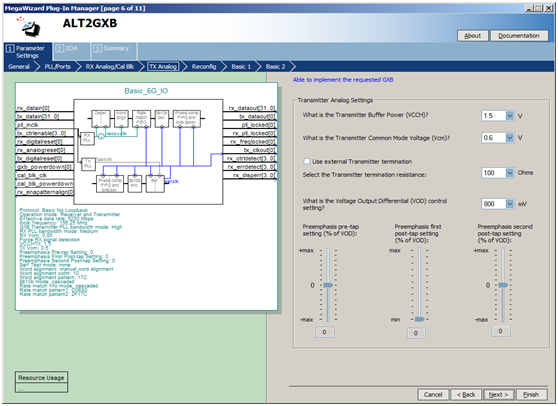

图5:发送端模拟设置

图4位接收端模拟和校准模块配置界面,该界面基本默认设置即可。图5是发送端模拟设置,除非想使用高级的应用比如预加重或者接收端均衡等,否则也请默认设置。

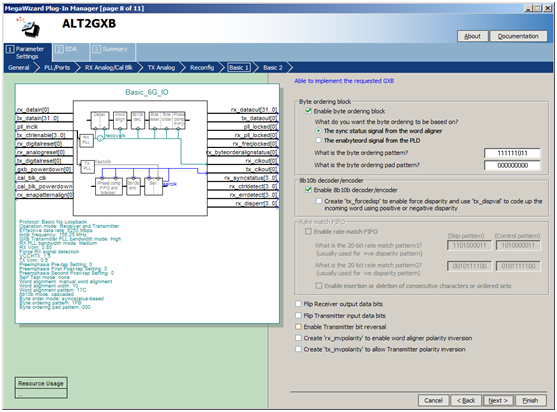

图6:协议设置之Basic1设置界面

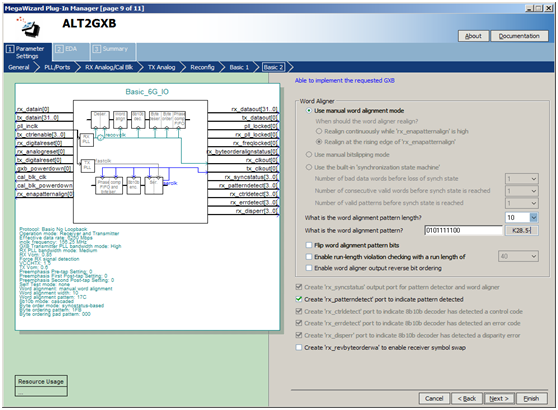

图7:协议设置之Basic2设置界面

图6是协议设置之Basic1设置界面,使能8B/10B编解码和byte ordering模块。对于byte ordering模块使能基于“The sync status signal from the word aligner”。

注:This means that after word aligner automatically signals for byte ordering to begin once the word boundary has been found.

另外byte ordering模块的pattern码和pad pattern码默认即可,这其实就是本文开始时提到的K27.7码。

图7时协议设置之Basic2设置界面,由于之前已经使能了Byte Ordering模块,所以这里的word alignment模块已经被自动使能了。其它默认即可,控制码默认就是K28.5。

到此,GXB设置基本完成了,只是不知道为何Single模式即位宽16-bit以内无法使能Byte Ordering模块。

仿真结果说明

图8:仿真结果波形图(一)

查看仿真结果,放大波形图如图8所示,0 ns到160 ns这段为收发器复位和上电控制流程:

l 60 ns左右,gxb_powerdown信号被复位逻辑de-assert了

l 74 ns左右,pll_locked信号变高显示发送PLL锁定到输入时钟了。由此,大概在80 ns左右的时候,tx_digitalreset被复位逻辑de-assert了

l 同时,在gxb_powerdown变低以后,rx_analogreset被复位逻辑在67 ns左右置低

l rx_analogreset被置低后,rx_pll_locked信号大概在80 ns左右变高,表示接收PLL已经锁定到输入参考时钟

l rx_pll_locked信号变高以后,大概在183 ns左右rx_freqlocked也被拉高,显示输入参考时钟和接收PLL时钟之间的PPM差异在规定的限制范围内。在390 ns,或者32个周期后,rx_digitalreset被释放,这样接收器才能正常操作了

经历以上流程后,发送器和接收器可以开始准备发送和接收工作了。

图9:仿真结果波形图(二)

查看仿真波形图380 ns到500 ns,如图9所示。从图8和图9可知,发送器在复位阶段是发送idle码K28.4(十六进制的9C),此时tx_ctrlenable为高。

l 在394 ns,发送器停止发送idle码,转而开始发送字对齐控制符,即K28.5(十六进制BC),注意此时tx_ctrlenable依然为高

l 445 ns,发送K27.7控制符(十六进制FB),用于接收器中Byte Ordering模块,注意此时tx_ctrlenable依然为高

l 450 ns,tx_ctrlenable为低,发送器开始发送数据

图10:仿真结果波形图(三)

查看仿真波形图470 ns到560 ns,如图10所示。注意接收器的rx_patterdetect,rx_syncstatus,rx_byteorderalignstatus,rx_dataout,rx_ctrldetect,rx_disperr和rx_errdetect信号。

l 在485 ns,当word aligner发现K28.5控制符的时候,它通过rx_syncstatus标示并对齐字边界。同时,rx_patterdetect表示在16-bit半字边界找到了对齐码。需要注意的是rx_patterdetect会变低一旦没有了对齐码,而rx_syncstatus变高后会一直保持不变直到重新复位。

l 同时在485 ns,注意rx_dataout的值,会发现其为BCBC9C9C。由于发送器发送的是9C9C9C9C和BCBCBCBC,所以这就意味着16-bit半字对齐失败,不过用户可以通过逻辑对齐,或者通过Byte Ordering模块自动对齐。

l 在535到550 ns之间,可以看到接收器收到了byte ordering控制符K27.7,并且正确地对齐了输出数据的32-bit边界。可以看到此时rx_byteorderalignstatus信号被拉高,同时上一个字的MSBs处被插入了0000。

l 在550 ns处,接收器开始将计数器值放置到rx_dataout端口,同时rx_ctrldetect为低

分析及结论

。

参考

[1] http://bbs.ednchina.com/BLOG_ARTICLE_220850.HTM 在ModelSim SE版本中提取Altera库

[2] 为ModelSim独立版本提取ALTERA库(续)

[3]