【技术分享】改善代码风格,利用寄存器平衡优化时序

0赞1.3.4 通过寄存器平衡来优化时序

第四个用于提高时序性能的策略我们称其为寄存器平衡,从概念上来讲,该方法是将任两个寄存器之间的逻辑重新平均分配,以最小化这两个寄存器之间的最大延时。这个技巧通常用于关键路径和其相邻路径之间逻辑分布高度不平衡的情况。我们知道时钟速度只取决于最差路径,所以只需实施很小的改动就能成功地重新平衡关键逻辑分布。

现在很多综合工具都提供了寄存器平衡的优化选项,这个特性使得综合工具可以以预测的方式事先识别特定结构以及重新定位分配寄存器周围的逻辑。这个优化选项对于类似乘法器这类普通结构非常有用,但是在不同设计中还是有限制,或者说当工具无法识别用户逻辑功能时将不会更改用户逻辑。根据这个技术的特点,一般只有比较昂贵的综合工具才具备这项优化选项。所以掌握这个技术的概念以及在用户逻辑结构中重新分配逻辑的能力将非常重要。

我们来讨论下面这段代码,这是一个加法器的例子,加法器的三个输入位宽为8-bit:

module adder( output reg [7:0] Sum, input [7:0] A,B,C, input clk); reg [7:0] rA,rB,rC; always @ (posedge clk) begin rA<=A; rB<=B; rC<=C; Sum<=rA+rB+rC; end endmodule

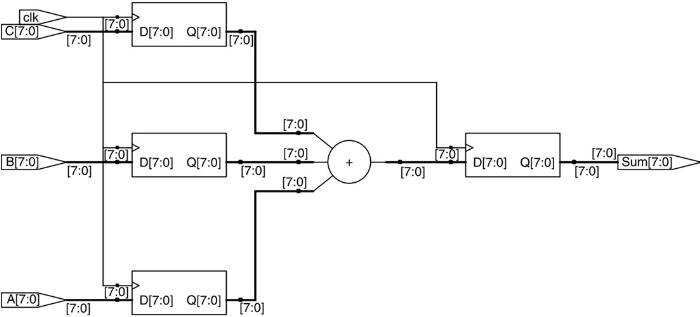

第一级寄存器包括rA、rB和rC,第二级寄存器是Sum。这两级寄存器之间是一个三输入加法器,而输入和第一级寄存器之间没有任何逻辑(假定前一个模块输出到本模块输入之前经过了寄存器寄存),如图1-9所示。

图1-9:加法器输入输出寄存

如果关键路径定义为通过加法器的路径,那么关键路径上的一些逻辑可以往后移动一级,那么上述两级寄存器的逻辑负载将会得到平衡。如下述代码所示,我们将其中一个加法操作往后移动一级:

module adder( output reg [7:0] Sum, input [7:0] A,B,C, input clk); reg [7:0] rABSum,rC; always @ (posedge clk) begin rABSum<=A+B; rC<=C; Sum<=rABSum+rC; end endmodule

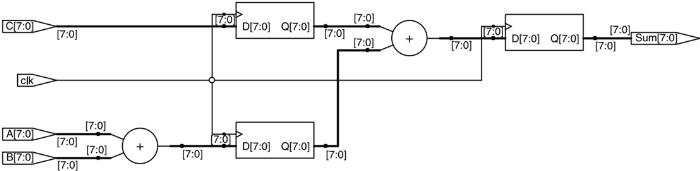

我们看到将一个加法操作从输入和第一级寄存器之间往后移动了一级,这样平衡了流水线各级之间的逻辑分布,从而减小了关键路径,如图1-10所示。所以我们可以得出这样的结论,即寄存器平衡是通过移动关键路径和相邻路径上的组合逻辑来提升设计的时序性能。

图1-10:寄存器平衡