【技术分享】改善代码风格,通过重组关键路径优化时序

0赞

发表于 1/15/2014 3:15:55 PM

阅读(6680)

1.3.5 通过关键路径重组来优化时序

第五个用于提高时序性能的策略我们称其为路径重组,即通过重组数据流上的路径达到最小化关键路径的目的。这个技巧通常用于关键路径是由多个路径组合而成的场合,而且这些被组合的路径之间又可以重组相互之间的先后顺序。通过这样简单的顺序重组,可以使得寄存器之间的关键路径被拉得更近。使用这个策略的时候,我只需关注任何给定的寄存器之间的逻辑路径。举例来说,我们先来看看下述代码:

module randomlogic( output reg [7:0] Out, input [7:0] A,B,C, input clk, input Cond1,Cond2); always @ (posedge clk) if (Cond1) Out<=A; else if (Cond2&&(C<8)) Out<=B; else Out<=C; endmodule

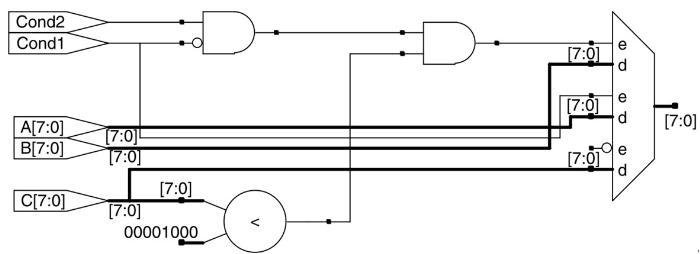

在这个例子中,首先我们假设关键路径是C和Out之间的路径,这个路径包括了比较器、两个与门以及一个多路选择器,如图1-11所示。

图1-11:过长的关键路径

如果我们假设前面例子中的条件判决不是互斥的,那么我们可以将上述代码修改如下所示:

module randomlogic( output reg [7:0] Out, input [7:0] A,B,C, input clk, input Cond1,Cond2); wire CondB=(Cond2&!Cond1); always @ (posedge clk) if (CondB&&(C<8)) Out<=B; else if (Cond1) Out<=A; else Out<=C; endmodule

通过重新组织代码,我们将关键路径上的一个门电路移出关键路径,如图1-12所示。所以如果我们非常注意代码是如何实现具体功能的时候,我就可以对时序性能施加非常直接的影响。根据以上分析,我们可以得出这样的结论,即通过重组组成关键路径的路径,使关键路径中的某个路径距离目的寄存器更近,这样可以使设计的时序性能得到改善。

图1-12:通过逻辑重组减小关键路径