榨干I2C时序

0赞榨干I2C时序

1.1. I2C-SCCB时钟

此处描述的I2C时序,是摄像头SCCB的通信时序。不过其实和I2C时序没啥区别,就是换了个名字而已。。。

很重要的一点,我以前就讲过,I2C要上拉电阻,典型值4.7K,不然会出问题。。。其次,通信频率。。。手册规定400KHz以内,这跟业界保持了一致。。。

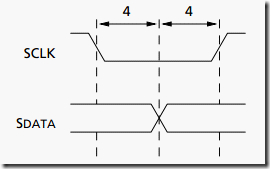

如上图所示,Tmack=1.25us=800KHz----所以SCLK最多为400KHz。

准确的采样点应该是:1.25us+SCLK高电平的中点;或者直接说,是SCLK高电平的中点。

1.2. I2C通信时序描述

(1)数据传输:SCL为高电平,SDA保持稳定,如下图所示:

(2)数据改变:SCL位低电平,SDA才能改变传输的bit,这个非常重要,因为I2C在高电平读取数据。

(3)开始信号:SCL为高电平时,SDAT由高电平向低电平跳转,开始传送数据

(4)结束信号:SCL为高电平时,SDAT由低电平向高电平传输,结束传送数据

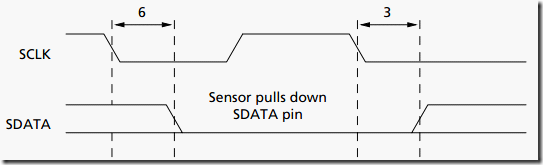

(5)应答信号:

<a>在9th clock,若I2C发出ACK,SDA会被拉低;

<b>在9th clock,若I2C没有ACK,SDA会被置高,从而Master Repeat。

1.2.1. I2C写流程

(1)Master发出START信号--开始信号

(2)Master发出I2C ADDR(7bit)和W操作0( 1bit)信号,等待ACK

(3)Slave发送ACK

(4)Master发送reg addr(8bit),等待ACK

(5)Slave发送ACK

(6)Master发送reg data(8bit),等待ACK

(7)Slave发送ACK

(8)Master发出STOP信号--结束信号

备注:操作(6)(7)可以连续进行,即顺序写入寄存器,时序仿真图如下所示:

1.2.2. I2C读流程

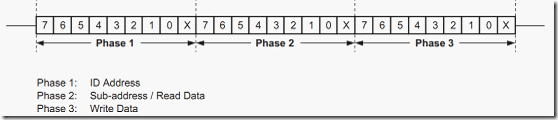

如上图所示,读取分为2个过程,过程1制定寄存器地址,过程2读取寄存器数据,总的流程如下所示:

(1)Master发出START信号--开始信号

(2)Master发出I2C ADDR(7bit)和W操作0( 1bit)信号,等待ACK

(3)Slave发送ACK

(4)Master发送reg addr(8bit),等待ACK

(5)Slave发送ACK

(6)Master发出STOP信号--结束信号

(7)I2C初始化状态

(8)Master发出START信号--开始信号

(9)Master发出I2C ADDR(7bit)和R操作1( 1bit)信号,等待ACK

(10)Slave发送ACK

(11)Slave发送reg data(8bit),等待ACK

(12)Master发送ACK

读取寄存器数据的时序仿真图,如下所示:

1.3. 总结

一个I2C写入的时序,需要8个状态的转移;而一个I2C读取的时序,需要12个状态的转移,加上1个初始化状态,一个完整的I2C时序,共需要21个状态转移。最重要的一点,是要保证SCK高电平是,SDA已经处于稳定期;而读取Slave数据的时候,最好在SCK高电平中点,这样读取的也是稳定期的数据!

顺便说一句:Terasic的I2C时序,简直就是LAJI!!!

顺便再说一句:我写的三段式状态机,Quartus II好像不能识别 不能给我状态转移图