FPGA快速中值滤波的实现的思维

0赞

发表于 2013/6/25 下午9:00:07

阅读(5772)

FPGA快速中值滤波的实现的思维

快速排序算法:

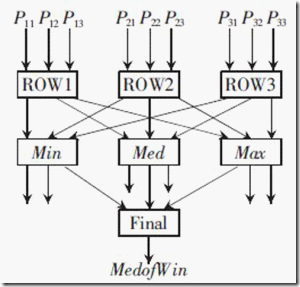

1) 分别比较每行,分别得到3个的Max,Med,Min,得到新的矩阵。

2) 分别比较3个Max,3个Med,3个Min。

a) Max的Max肯定是9个数的最大值,9th不是中值,舍去。

b) Min的Min肯定是9个数的最小值,1th不是中值,舍去。

c) Med中的Max至少大于5个数,不是中值,舍去。

d) Med中的Min至少小于5个数,不是中值,舍去。

e) 同时剩下5个数中,Max的较大的数,和Min中较小的数肯定不是中值,剩下三个数,Max_min, Med_med, Min_max

3) 比较Max_min, Med_med, Min_max,得到的中值,就是9个数的中值。

然后用verilog实现,其实这需要耗费很大的逻辑,如果要做到实时的话,基本的思路表示采用状态机,而是采用流水线!!