【红色飓风Nano二代测评】Xilinx DCM PLL区别及PLL使用方法

0赞Xilinx DCM PLL区别及PLL使用方法

—CrazyBingo

—20140505

延续上一篇《Xilinx DCM IPCore研究及使用方法》,在该篇基础上,对比DCM与PLL区别,并且介绍PLL的功能,对于Altera PLL的差异,及使用方法。。。

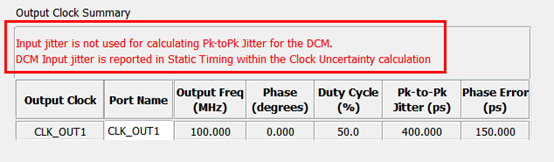

在上一篇定制DCM的时候,遇到过一个警告。。。虽然目前对结果没有产生影响吗,但是看着真的很不爽啊!!!有强迫症。。同时又不知道如何解决(当然如果用原语,警告都看不到呵呵),如下所示:

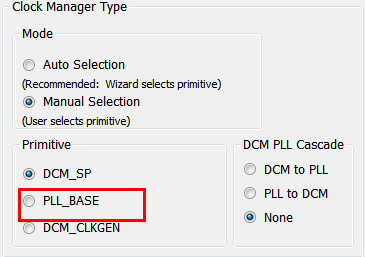

突然,有一群友告诉我说,DCM输出的时钟稳定性不强,比如在驱动显示VGA的时候,由于时钟抖动,会有水纹波现象。。。同时。。。指点了一下。。。默认是DCM的原因,是由于我选择了Auto Selection,我得选择Manual Selection,进一步选择PLL IPCore,如下所示:

同时,群友又告诉我,一般我们使用PLL,在PLL实在不够用的时候,才会考虑使用DCM。。。好吧,我是懂非的懂,朦胧的接受了这个答案(有有人跟我说木有问题的),毕竟我进入Xilinx 才不到10小时,至于颠覆或逆袭,暂时没这个资格。。。所以,其他设置几乎不变,开始了PLL的旅程。

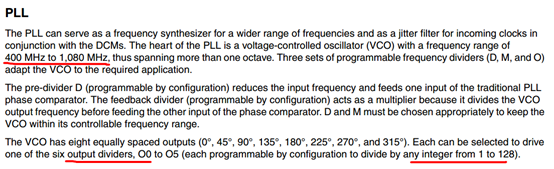

继续嗑Sparatan Guide关于PLL的简要介绍:

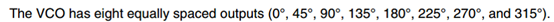

PLL的核心为VCO,即压控振荡器,能在400~1080MHz之间摆动,输出频率由D、M、O三个参数设定。基本的功能、参数啥的,基本与Altera的PLL一模一样。。不过Altera Cyclone II的PLL只能输出3个时钟,而Cyclone III/IV的PLL能输出5个输出。。但Spartan 的FPGA能输出6个时钟。。呵呵。。其他的用着再说。。。唯一不清楚的是这句话:

半天看不懂啥意思有木有?》》??

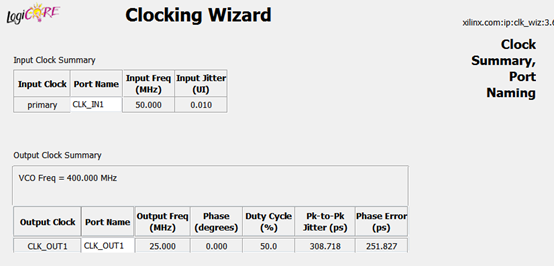

Okay,开始配置PLL输出25MHz,VGA驱动果断准备开始,如下:

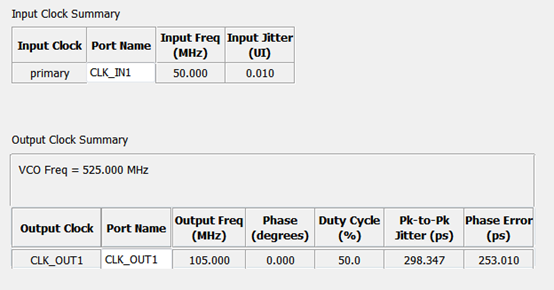

同时又生成了一个105MHz的时钟玩玩。。。1280*1024*60Hz是105MHz的。。

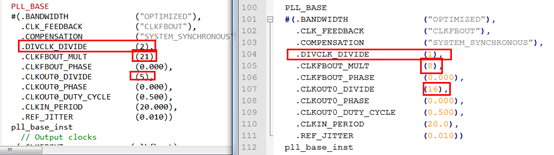

强迫症,邮箱研究Xilinx 原语了。。。拿这两个25MHz以及105MHz的sys_pll来做对比,如下所示:

作为为105MHz的原语,右边为25MHz的原语。分析区别与差异,得出以下结论:

(1)DEVCLK_DIVIDE为全局分频,比如PLL输出5个时钟,每一通道实现实现2分频,则参数为2

(2)CLKFBOUT_MULT为乘法因子

(3)CLKOUT0_DIVIDE为CLK0通道的除法因子

(4)CLKIN_ PERIOD = 20.000可见输入为50MHz

因此CLK0通道的时钟的值,计算如下:

CLK0 = CLKIN_PERIOD / DEVCLK_DIVIDE * CLKFBOUT_MULT / CLKOUT0_DIVIDE

= 50MHz / 2 * 21 / 5 = 105MHz(左边)

= 50MHz /1 * 8 / 16 = 25MHz(右边)

哈哈。反复测试。。一如既往的可以。。。第一次生成ipcore后,提取verilog代码。。今后打算在也不使用IPCORE来反复生成、修改IP了。。。

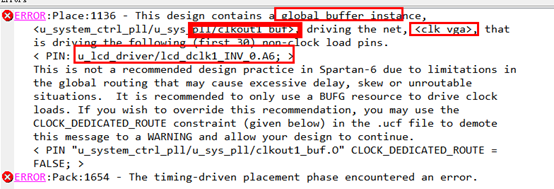

但又出现了一个新的问题。。。NND 。。。如下图所示:

意思就是说从PLL的Buffer输出的时钟,不能直接输出到外部。。由于VGA的lcd_dclk是直接输出到外部的。。

这里总结一下DCM与PLL的区别,仅以鄙人目前浅陋的见识:

(1) DCM只支持90、180、270相位,但PLL这方便更灵活宽泛

(2) DCM只支持2~16的小数分频,以及2倍频,但是PLL这方面更灵活宽泛

(3) DCM是用数字延时模块调理时钟,是纯数字的东西,用的灵活,占得面积小,噪声和jitter相对PLL大一些。

(4) PLL是模拟的,比DCM要浮躁,出来的钟也质量也高,但是比较复杂,占的面积也比DCM大

深入了解DCM:是基于Xilinx的其他系列器件所采用的数字延迟锁相环(DLL,Delay Locked Loop)模块。在时钟的管理与控制方面,DCM与DLL相比,功能更强大,使用更灵活。DCM的功能包括消除时钟的延时、频率的合成、时钟相位的调整等系统方面的需求。DCM的主要优点在于:

①实现零时钟偏移(Skew),消除时钟分配延迟,并实现时钟闭环控制;

②时钟可以映射到PCB上用于同步外部芯片,这样就减少了对外部芯片的要求,将芯片内外的时钟控制一体化,以利于系统设计。对于DCM模块来说,其关键参数为输入时钟频率范围、输出时钟频率范围、输入/输出时钟允许抖动范围等。

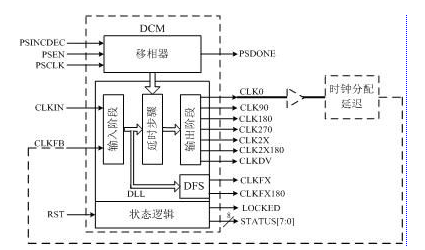

DCM共由四部分组成,如上图所示。其中最底层仍采用成熟的DLL模块;其次分别为数字频率合成器(DFS,Digital Frequency Synthesizer)、数字移相器(DPS,Digital Phase Shifter)和数字频谱扩展器(DSS,Digital Spread Spectrum)。不同的芯片模块的DCM输入频率范围是不同的

而PLL,无需多言,对于Altera FPGA驰骋5年而言,太熟悉了……