一种极度现实的SDRAM相位测试法

0赞一种极度现实的SDRAM相位测试法

对于初学者而言,SDRAM的驱动,一直都是望尘莫及,甚至可望而不可即。。。。而SDRAM的驱动,设计到一个驱动时钟,一个逻辑时钟,这两者的相位差,更是让很多人摸不着头脑。。。

特权曾经总结过SDRAM相位,不知道是不是很多人学会了,网址如下所示:http://wenku.baidu.com/link?url=7jZHX3gor2r2w8vCg9k4DjhmIgOxWTUFXcAuTp_930fgbjiavGJ4OPxYFI2fdeoJ7l-vCvfpMgE_KAfa-nJfhGvnSbDN0LTDXaUUvFnzuKy

坦白说,特权的计算方式我看过很多遍。。。。太烦人。。。。。。。

本人做的设计一般跟视频有关。。因此一直,一直采用经验值+SDRAM+VGA的显示效果,来推算出一个最适合当前板卡的一个相位值。。。。且说是一种极度现实的SDRAM相位测试法吧。。。。因为的确太贴近板卡本身了。。。。。

(1) 首先,经验值,我一般采用-90°的偏移时钟,一般情况下都OK

(2) 其次,在速度高了的时候,一般缩短偏移时钟,根据VGA/LCD的显示效果调整偏移相位角度。。。

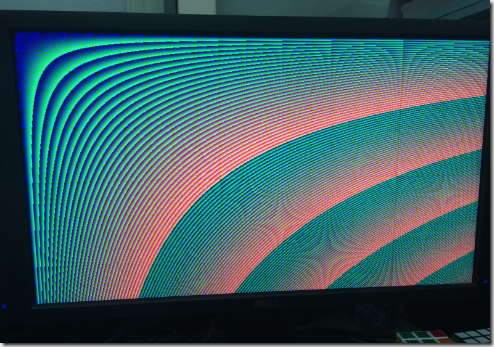

比如,如下图所示,是我100MHz的时候驱动SDRAM,并且在VGA上显示的效果,此时SDRAM CLK相位偏移-90°:

而当我把SDRAM的逻辑时钟提高到150MHz的时候,得到的VGA的显示效果,如下所示:

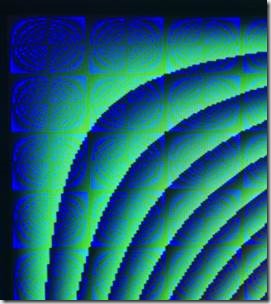

可能你不能看的很清楚,毕竟图片没有我直接在显示器上看到的分辨率大,于是我放大两个图的左上角给你看,请注意观察细节!!!!!,如下图所示:

仔细分析左右图,不难看出问题了吧,。。。右图很多像素在闪了。。。原因是由于时钟不匹配,从SDRAM中读取的时候,数据不够稳定。。。。。

其实想改善很简单。。。我将SDRAM CLK的偏移时钟改成-45°,问题就轻松地解决了。。。。呵呵呵。。。最后的结果完全匹配当前电路板。。。万无一失。。。

总结一下,很多人说图像出现闪点,这事什么原因。。。如下:

(1) LCD/VGA的输入数据,有效期中点必须与输出时钟的上升沿,确保终端读取稳定

(2) SDRAM的偏移时钟,根据实际板卡的设计进行调试,确保数据读取在稳定期

(3) 最终还不够理想的,对PLL的输出相位进行偏移,总会有最满意的一个点。。。