【SystemVerilog断言学习笔记2】断言的类型

0赞SystemVerilog中包含并发断言和即时断言两种类型的断言。所谓并发断言就是在时钟边沿对变量进行采样并完成测试表达式的计算,它可以在模块、接口、过程块或程序中定义。这里有一点是需要声明的,对于变量的采样值是时钟边沿前一时刻相应变量的值。而即时断言只能在过程块中定义的,测试表达式的计算跟Verilog HDL过程块中的行为一样,即一旦事件发生变化则表达式立刻被求值。接下来通过modelsim对这两类的断言进行仿真测试,给大家一个直观的理解。

1、并发断言

<1>打开modelsim仿真软件,然后点击“File—>New—>Project…“,出现如下对话框,为对话框填上工程名以及路径,其他默认,点击”OK“后会弹出询问是否创建工程路径的对话框,选择”是“。

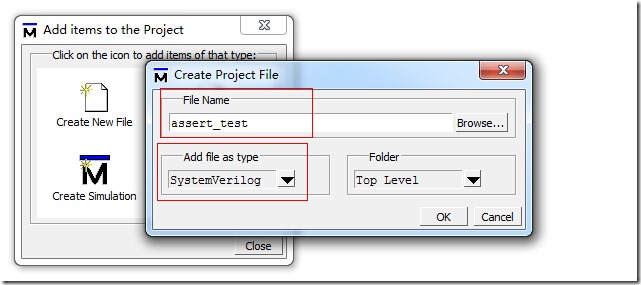

<2>在下面的对话框中点击“Create New File”以新建源文件。

<3>为对话框填上新建文件名以及文件类型选为“SystemVerilog”,然后点击“OK”,“Close”。。。

<4>为新建的sv文件编写SystemVerilog代码,如下所示:

/*******************************************************

作者 : CrazyBird

文件 : assert_test.sv

日期 : 2015-5-1

功能 : 并行断言

********************************************************/

`timescale 1ns/1ps

module assert_test(

output reg clk,

output reg a,

output reg b

);

// 时钟的产生

parameter PERIOD = 10;

initial

begin

clk = 0;

forever #(PERIOD/2)

clk = ~clk;

end

// 激励的产生

initial

begin

a = 0;

b = 1;

repeat(20)@(negedge clk)

begin

a = {$random()}%2;

b = {$random()}%2;

end

@(negedge clk);

$stop;

end

// 并行断言

a_cc: assert property(@(posedge clk) not(a&&b));

endmodule

该段代码断言信号a和信号b不能同时为1,否则断言失败。

<5>选择要编译的文件assert_test.sv,接着点击“Compile—>Compile Selected”,如果编译正确,transcript状态栏会提示编译成功,并且文件状态会由蓝色“问号”变为绿色“打钩”,如下图所示。

<6>编译成功后,接下来开始仿真。点击“Simulate—>Start Simulation…”,在弹出的对话框中,展开work,选择assert_test,然后“OK”。

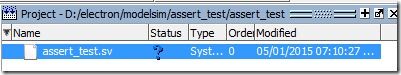

<7>将Object下的信号clk、a、b添加到波形中去,做法是选中信号clk、a、b,然后右键单击“Add to—>Wave—>Selected signals”,如下图所示:

<8>点击“Simulate—>Restart…”,“OK”,接着点击“Simulate—>Run—>Run –All”,再接着点击“Wave—>Zoom—>Zoom Full”,其波形如下所示:

<9>在transcript状态栏下会出现断言失败的信息,通过双击它,可在Wave中显示断言失败的地方,如下图所示:

# ** Error: Assertion error. # Time: 25 ns Started: 25 ns Scope: assert_test.a_cc File: D:/electron/modelsim/assert_test/assert_test.sv Line: 38 # ** Error: Assertion error. # Time: 35 ns Started: 35 ns Scope: assert_test.a_cc File: D:/electron/modelsim/assert_test/assert_test.sv Line: 38 # ** Error: Assertion error. # Time: 55 ns Started: 55 ns Scope: assert_test.a_cc File: D:/electron/modelsim/assert_test/assert_test.sv Line: 38 # ** Error: Assertion error. # Time: 105 ns Started: 105 ns Scope: assert_test.a_cc File: D:/electron/modelsim/assert_test/assert_test.sv Line: 38 # ** Error: Assertion error. # Time: 155 ns Started: 155 ns Scope: assert_test.a_cc File: D:/electron/modelsim/assert_test/assert_test.sv Line: 38 # ** Error: Assertion error. # Time: 205 ns Started: 205 ns Scope: assert_test.a_cc File: D:/electron/modelsim/assert_test/assert_test.sv Line: 38

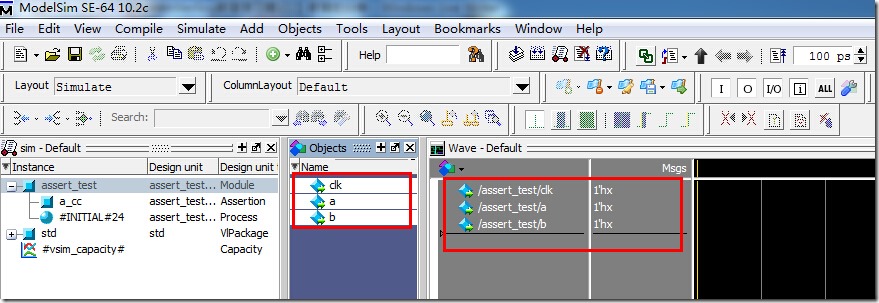

<10>也可以通过点击“View—>Coverage—>assertions”查看断言的情况,如下所示:

很明显,断言失败有6处地方。

2、即时断言

<1>操作基本跟上面的一样,即时断言的一个例子如下所示:

/*******************************************************

作者 : CrazyBird

文件 : assert_test.sv

日期 : 2015-5-1

功能 : 即时断言

********************************************************/

`timescale 1ns/1ps

module assert_test(

output reg clk,

output reg a,

output reg b

);

// 时钟的产生

parameter PERIOD = 10;

initial

begin

clk = 0;

forever #(PERIOD/2)

clk = ~clk;

end

// 激励的产生

initial

begin

a = 0;

b = 1;

repeat(20)@(negedge clk)

begin

a = {$random()}%2;

b = {$random()}%2;

end

@(negedge clk);

$stop;

end

// 即时断言

always_comb

begin

a_ia: assert (a&&b);

end

endmodule

该段代码断言信号a和信号b同时为1,否则断言失败。

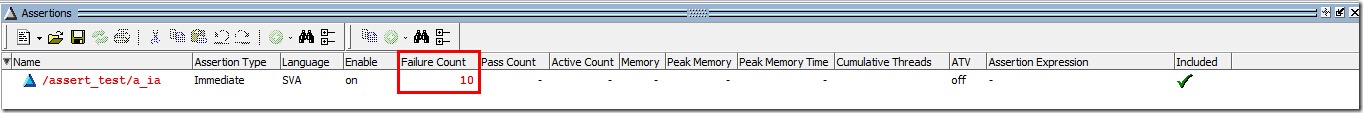

<2>其断言情况如下所示:

# ** Error: Assertion error. # Time: 0 ps Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41 # ** Error: Assertion error. # Time: 40 ns Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41 # ** Error: Assertion error. # Time: 60 ns Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41 # ** Error: Assertion error. # Time: 70 ns Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41 # ** Error: Assertion error. # Time: 110 ns Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41 # ** Error: Assertion error. # Time: 120 ns Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41 # ** Error: Assertion error. # Time: 130 ns Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41 # ** Error: Assertion error. # Time: 160 ns Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41 # ** Error: Assertion error. # Time: 170 ns Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41 # ** Error: Assertion error. # Time: 180 ns Scope: assert_test.a_ia File: D:/electron/modelsim/assert_test/assert_test.sv Line: 41

很明显,断言失败有10处地方。

关于断言的类型先介绍到这,待续!!!