【SystemVerilog断言学习笔记6】禁止属性的使用

1赞

发表于 5/7/2015 7:33:00 PM

阅读(4885)

当我们期望属性永远为假时,可以用关键字“not”来禁止属性,即当属性为真时断言失败。接下来验证“not”是如何运作的。

测试代码:

/*******************************************************

作者 : CrazyBird

文件 : assert_test2.sv

日期 : 2015-5-7

功能 : 禁止属性“not”的测试

********************************************************/

`timescale 1ns/1ps

module assert_test2(

output reg clk,

output reg a,

output reg b

);

// 产生时钟

parameter PERIOD = 10;

initial

begin

clk = 0;

forever #(PERIOD/2)

clk = ~clk;

end

// 产生激励

initial

begin

a = 1;

b = 1;

repeat(20)@(negedge clk)

begin

a = {$random()}%2;

b = {$random()}%2;

end

@(negedge clk);

$stop;

end

// 建立序列

sequence s1;

a ##2 b;

endsequence

// 建立属性

property p1;

@(posedge clk) not(s1);

endproperty

// 断言属性

a1 : assert property(p1);

endmodule

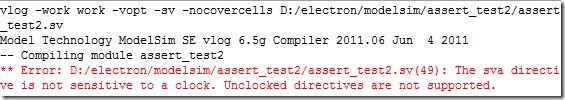

注意“not”所在的位置,如果是下面的写法,编译将报错:

// 建立序列

sequence s1;

a ##2 b;

endsequence

// 建立属性

property p1;

not(@(posedge clk) s1);

endproperty

或者

// 建立序列

sequence s1;

@(posedge clk) a ##2 b;

endsequence

// 建立属性

property p1;

not(s1);

endproperty

测试结果:

# ** Error: Assertion error. # Time: 25 ns Started: 5 ns Scope: assert_test2.a1 File: D:/electron/modelsim/assert_test2/assert_test2.sv Line: 49 # ** Error: Assertion error. # Time: 55 ns Started: 35 ns Scope: assert_test2.a1 File: D:/electron/modelsim/assert_test2/assert_test2.sv Line: 49 # ** Error: Assertion error. # Time: 65 ns Started: 45 ns Scope: assert_test2.a1 File: D:/electron/modelsim/assert_test2/assert_test2.sv Line: 49 # ** Error: Assertion error. # Time: 105 ns Started: 85 ns Scope: assert_test2.a1 File: D:/electron/modelsim/assert_test2/assert_test2.sv Line: 49 # ** Error: Assertion error. # Time: 115 ns Started: 95 ns Scope: assert_test2.a1 File: D:/electron/modelsim/assert_test2/assert_test2.sv Line: 49 # ** Error: Assertion error. # Time: 185 ns Started: 165 ns Scope: assert_test2.a1 File: D:/electron/modelsim/assert_test2/assert_test2.sv Line: 49

很明显,当时钟上升沿到来时,若a为高电平,2个时钟周期后,若b也为高电平,则断言失败,且失败标注在序列的结束位置。当时钟上升沿到来时,若a为低电平,则断言直接成功;若a为高电平,2个时钟周期后b为低电平,则断言成功。这刚好跟“a ##2 b”的属性相反,故验证了“not”是可以禁止属性的。

待续~~~