【原创】Spartan6之蛋疼的时钟管理模块

0赞忙了两个多月的毕业设计,有好长的一段时间没写过博客了。不过,在做毕设的过程中学到很多的东西,包括代码规范、文档规范、对设计的优化技巧等,最后也获得了相应的回报---毕设被评为优秀和创新。以为毕设搞定后就会很轻松,但我错了,事情又被排满了。呵呵,看来我只能全部接受了。

最近,实验室里的一个师妹准备用Xilinx的Spartan6系列FPGA做图像处理,由于她之前是用VC++做的图像处理,所以对她来说直接从软件到硬件的过渡很有难度。后来,实验室的老师就叫我帮忙搞一下。哈哈,搞就搞,毕竟是一个不错的学习机会啊。

在完成图像处理的框架之前,时钟的管理必须要做好。于是,开始测试了时钟管理模块,但是遇到了困难,经过查找资料,一一解决了。现在来看看是怎么回事?

1、首先是时钟管理模块IP的调用,下面是参数设置。输入时钟为50MHz,输出时钟有两个,分别为54MHz和108MHz。

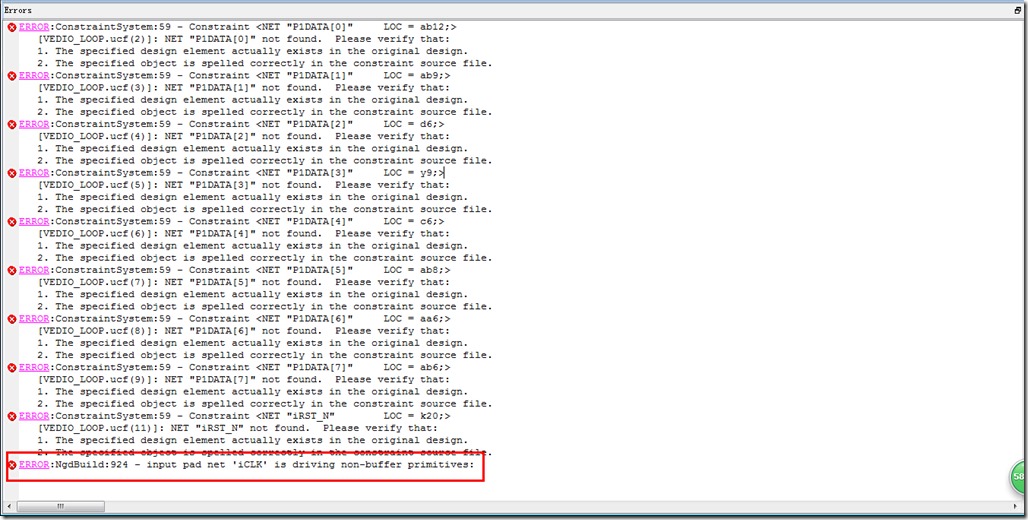

2、接着对设计进行综合,却发生了下面的错误。

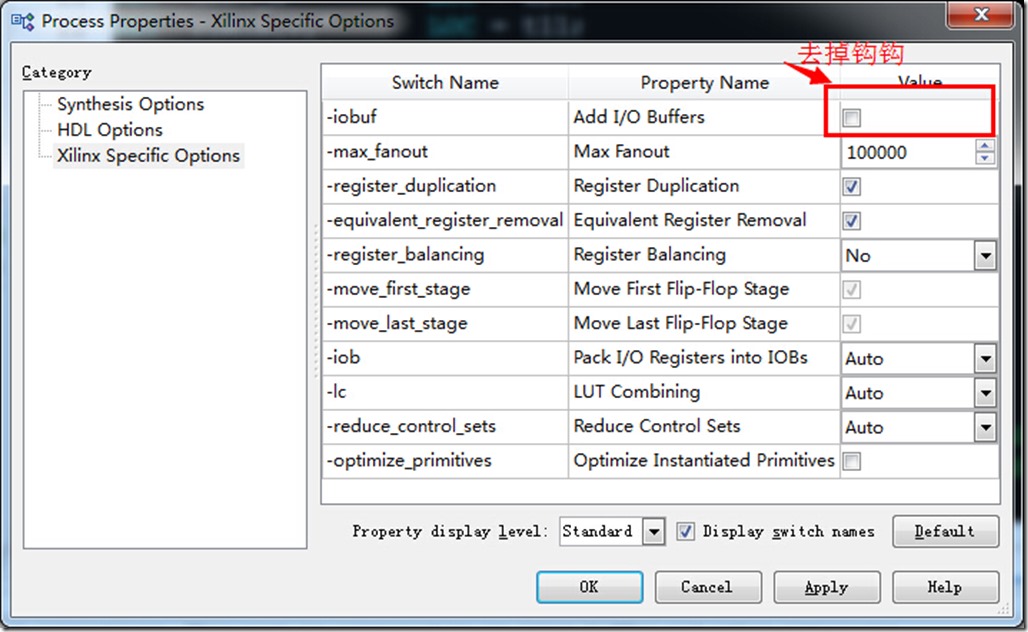

3、在网上找了一下解决办法,说可以通过右击Synthesize-XST,选择Process Properties,在弹出的对话框中切换到Xilinx Specific Options选项卡,将第一项Add I/O Buffers中的钩钩去掉,OK。

4、然后再进行综合,发现设计通过了综合。接着对设计进行布局和布线,很不幸,又出现问题了。(问题真多,记得之前玩过两个月Altera的FPGA时却没这么多问题!)既然问题来了,那就一个个击破。看到图中的最后一个错误,说是“iCLK”正在驱动没有buffer的原语,好像跟第三步的处理相反了。也许,一开始解决问题的思路就错了。于是,开始寻找其他解决办法并把第三步的钩钩打上。。。。

5、打开IP核,从新看下里面的参数。将下图的Source下选为Global buffer。然后,对设计进行综合没问题。

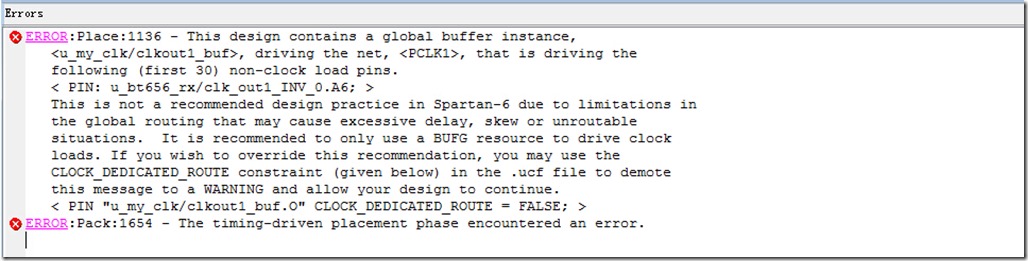

6、紧接着对设计进行布局布线,还是出错了,如下图。

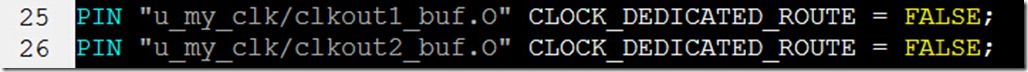

7、为了解决第六步中的错误,只要在引脚约束文件中添加如下的语句就可以了。

这样,关于时钟管理模块的问题解决了,终于可以开始下一步工作了。开心中。。。。