【原创】一个完整的vivado工程搭建

2赞记得前段时间玩了一下vivado,现在开始有点渐渐忘了。趁着没彻底忘记,赶紧做下笔记。看来,岁月真的是一把杀猪刀,人越老,记性就越差。今天,第一篇关于vivado的文章是vivado工程的搭建。

本篇博文所用到的软件是vivado2014.4,用到的开发板是zybo,并以一个简单的流水灯例子进行试验。

一、首先,打开vivado软件,主界面如图1所示。

图1 打开vivado软件

二、点击“Create New Project”,在弹出的新建工程向导中点击“Next”,弹出设置工程名和工程路径的对话框,如图2所示。在“Project name”项中输入工程名water_led,在“Project location”项中输入或选择工程的路径,而“Create project subdirectory”如果勾选,则会在所选的工程路径中创建一个名字与工程名一样的用于存放工程的新文件,否则直接在所选工程路径下创建工程。

图2 设置工程名和工程路径

三、点击“Next”,弹出选择工程类型的对话框,如图3所示。选择RTL类型,请注意RTL类型下有“Do not specify sources at this time”选项,意思是在新建工程过程中不指定源文件。假设不勾选该选项,后面将会连续弹出新建或添加已存在的源文件、添加已存在的IP、新建或添加已存在的约束文件,分别如图4、图5和图6所示。由于现在不需要新建或添加任何文件,故这里勾选“Do not specify sources at this time”。

图3 选择工程类型

图4 新建或添加已存在的源文件

图5 添加已存在的IP

图6 新建或添加已存在的约束文件

四、点击“Next”,弹出选择器件型号的对话框,如图7所示。如果所用开发板是评估板的话,其型号可在“Boards”选项卡中进行选择,如图8所示。而本次试验的开发板并不是评估板,故在“Parts”选项卡中进行器件型号的选择。图7所示,器件家族“Family”选zynq-7000,封装“Package”选clg400,速度等级“Speed grade”选-1,温度等级“Temp grade”选商业级C。

图7 选择器件型号

图8 选择评估板器件型号

五、点击“Next”、“Finish”完成工程的创建。创建工程后的主界面如图9所示,其中左侧面板是设计流程的管理,从源文件的添加到综合、仿真、布局布线、到最后板级调试,都可以通过点击相应的按键来完成;中间上面的面板是工程文件的管理;右侧面板是工程信息总结,包括工程的基本信息、综合实现所消耗的资源信息等;底部面板是各种信息的输出,包括编译信息、报告等。

图9 新建工程后vivado主界面

六、在vivado主界面左侧面板点击“Add Sources”按键为工程新建源文件,如图10所示,选择“Add or create design sources”,点击“Next”。

图10 新建源文件1

七、在弹出的对话框中,点击“Create File...”,文件类型“File type”选Verilog,文件名为water_led,如图11所示。点击“OK”、“Finish”、“OK”、“Yes”,完成Verilog源文件的新建。

图11 新建源文件2

八、为water_led.v添加实现流水灯的代码,如程序清单1所示。由于clk引脚连接到125MHz时钟下,故延时0.5s需要62500000个时钟周期。

程序清单1

/***************************Copyright***********************************

** CrazyBird

** http://blog.chinaaet.com/crazybird

**

**-----------------------File Infomation--------------------------------

** FileName : water_led.v

** Author : CrazyBird

** Data : 2015-11-22

** Version : v1.0

** Description : led display as water

**

***********************************************************************/

// synopsys translate_off

`timescale 1 ns / 1 ps

// synopsys translate_on

module water_led

#(

parameter C_DATA_WIDTH = 4

)

(

input rst,

input clk,

output [C_DATA_WIDTH-1:0] led_data

);

//-------------------------------------------

// 0.5s delay

localparam DELAY_TOP = 26'd62500000; // delay 0.5s

reg [25:0] cnt; // counter

always @(posedge clk or posedge rst)

begin

if(rst == 1'b1)

cnt <= 26'd0;

else if(cnt < DELAY_TOP-1'b1)

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

wire cnt_done = (cnt == DELAY_TOP-1'b1); // count done flag of 0.5s

//-------------------------------------------

// led display as water

reg [C_DATA_WIDTH-1:0] led_data_temp;

always @(posedge clk or posedge rst)

begin

if(rst == 1'b1)

led_data_temp <= {{(C_DATA_WIDTH-1){1'b0}},1'b1};

else if(cnt_done == 1'b1)

led_data_temp <= {led_data_temp[C_DATA_WIDTH-2:0],led_data_temp[C_DATA_WIDTH-1]};

end

//-------------------------------------------

// data output

assign led_data = led_data_temp;

endmodule

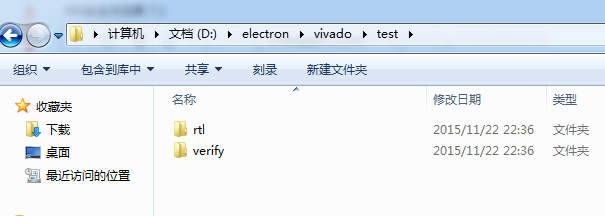

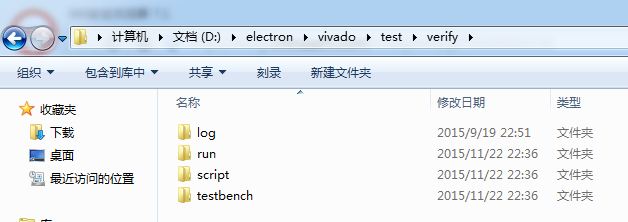

//****************************End File**********************************九、接下来对water_led模块进行仿真。在这里采用以前博文中介绍的验证平台进行仿真来验证设计的确定性。验证平台的组织结构如图12和图13所示。

图12 验证平台组织结构1

图13 验证平台组织结构2

十、将water_led.v文件放在rtl文件夹中,将测试文件testbench.v放在testbench文件夹中,其中testbench.v的代码如程序清单2所示。

程序清单2

/********************************Copyright****************************** ** CrazyBird ** http://blog.chinaaet.com/crazybird ** **----------------------------File Infomation--------------------------- ** FileName : testbench.v ** Author : CrazyBird ** Data : 2015-11-22 ** Version : v1.0 ** Description : testbench of water_led module ** ***********************************************************************/ // synopsys translate_off `timescale 1 ns / 1 ps // synopsys translate_on module testbench; //--------------------------------------- // Variable definitions reg rst; reg clk; wire [3:0] led_data; //--------------------------------------- // Clock generator parameter CLK_CYCLE = 8; // 125MHz initial begin clk = 0; forever #(CLK_CYCLE/2) clk = ~clk; end //-------------------------------------- // Module instantiation water_led #( .C_DATA_WIDTH(4) ) u_water_led ( .rst (rst ), .clk (clk ), .led_data (led_data ) ); //-------------------------------------- // Module initialization initial begin rst = 1; #(CLK_CYCLE*10); rst = 0; #(CLK_CYCLE*10000); $stop; end endmodule //****************************End File**********************************

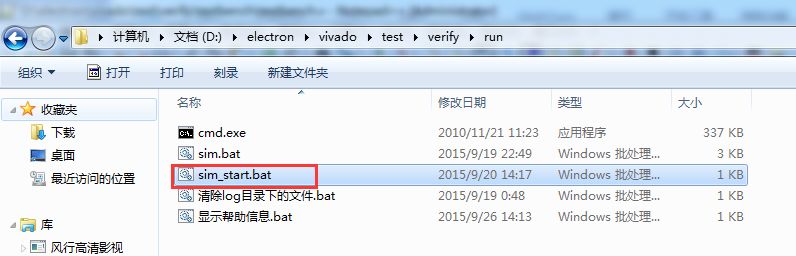

十一、为了减少仿真的时间,将water_led模块中的DELAY_TOP=26’d62500000改为DELAY_TOP=26’d500。接着修改验证平台run目录下的sim_start.bat批处理文件,如图14所示和程序清单3所示。以图形界面的形式启动modelsim,且无需加载任何器件库。

图14 修改sim_start.bat批处理文件

程序清单3

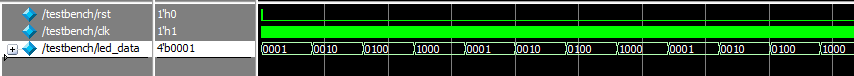

call sim -gui

十二、双击sim_start.bat批处理文件,启动modelsim仿真软件,仿真结果如图15所示。很显然,led在做流水运动,因此流水的功能是正确的。

图15 仿真结果

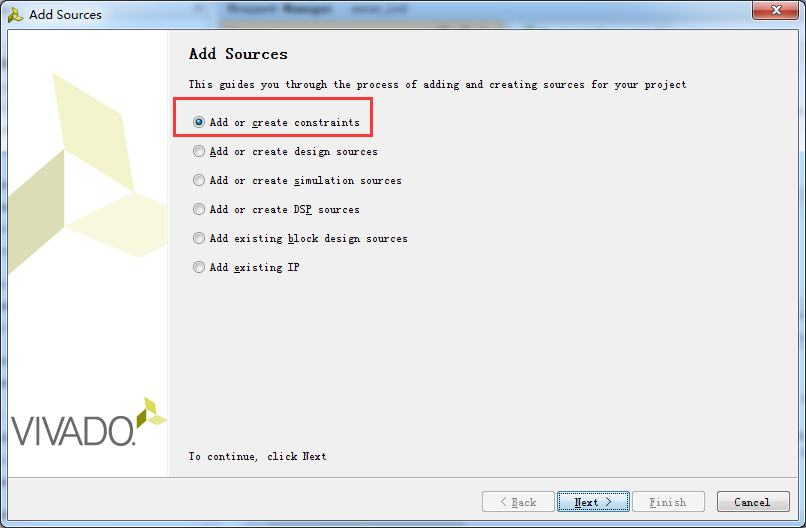

十三、接着新建约束文件对管脚进行约束。在vivado主界面左侧面板点击“Add Sources”按键为工程新建约束文件,如图16所示,选择“Add or create constraints”,点击“Next”。

图16 新建约束文件1

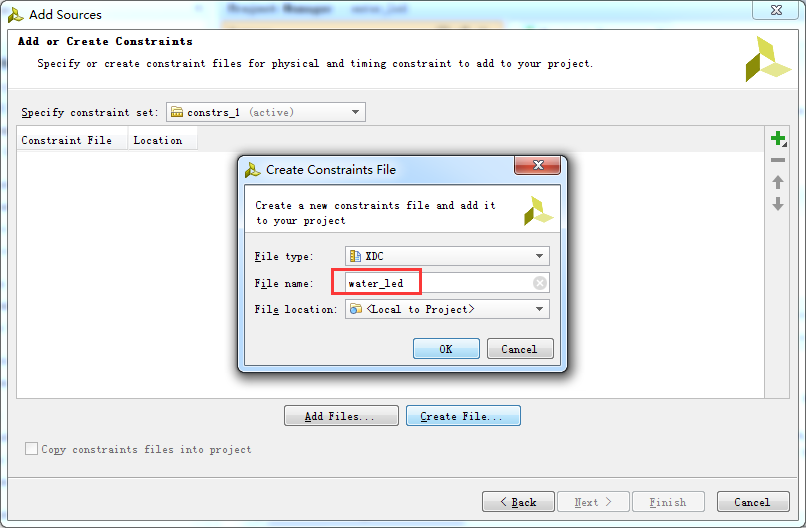

十四、在弹出的对话框中,点击“Create File...”,文件类型“File type”选XDC,文件名为water_led,如图17所示。点击“OK”、“Finish”,完成约束文件的新建。

图17 新建约束文件2

十五、为water_led.xdc添加约束代码,如程序清单4所示。

程序清单4

set_property PACKAGE_PIN L16 [get_ports clk]

set_property PACKAGE_PIN Y16 [get_ports rst]

set_property PACKAGE_PIN M14 [get_ports {led_data[0]}]

set_property PACKAGE_PIN M15 [get_ports {led_data[1]}]

set_property PACKAGE_PIN G14 [get_ports {led_data[2]}]

set_property PACKAGE_PIN D18 [get_ports {led_data[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports {led_data[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_data[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_data[2]}]

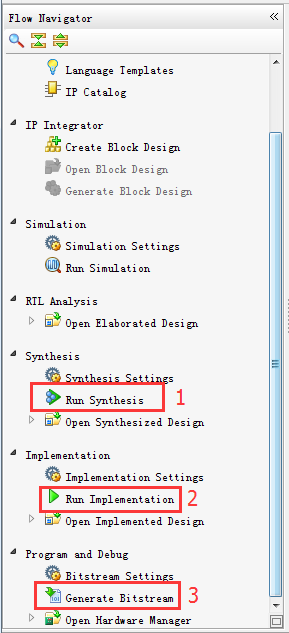

set_property IOSTANDARD LVCMOS33 [get_ports {led_data[3]}]十六、接下来对设计分别进行综合、实现、生成bit流文件(记得将water_led模块的DELAY_TOP改回26'd62500000),如图17所示。当然,也可以直接点击第三步“生成bit流”完成整个工程的编译。如果编译过程中出现错误,请返回检查,这里就不多阐述了。

图17 工程编译流程

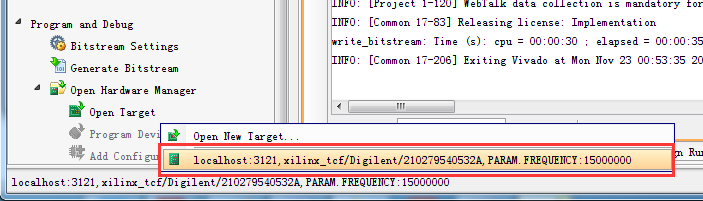

十七、生成bit流文件后就可以将其下载到zybo开发板上运行了。首先,将zybo开发板正确与电脑进行连接。接着打开目标器件,如图18所示。

图18 打开目标器件

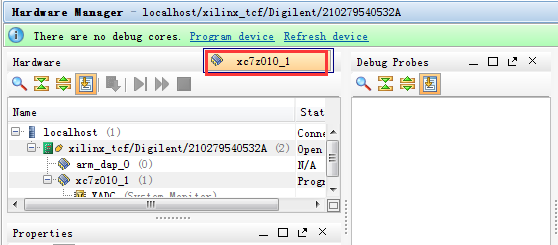

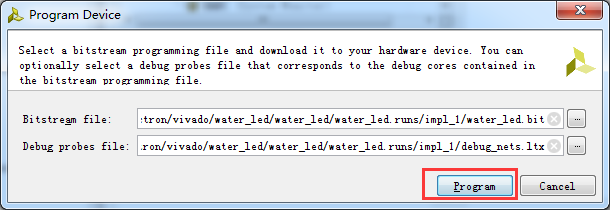

十八、在弹出的对话框中选择“Program device”——>“xc7z010_1”,如图19所示。然后点击“Program”,如图20所示。编程器件之后,zybo开发板上的四盏灯就像流水一样流动起来了。

图19 编程器件1

图20 编程器件2

第一个完整的vivado工程就这样完成了,是不是很简单呢?呵呵~~~