vivado逻辑分析仪的使用

0赞vivado逻辑分析仪的使用

前言:

一直在犹豫要不要把这篇半成品放上来,使用vivado逻辑分析仪时,刚开始的体验还是很愉快的,最近就一直出问题:在XP系统下,Hardware Manager的向导跑不动,处于循环等待的状态,这可能是电脑硬件配置低的原因。在工作站上跑的时候,总是无法Refresh Device,看错误提示是无法和ila ip核建立通信链接。

总而言之,最近在做设计的时候,出了问题也没法借助逻辑分析仪进行Debug,相当郁闷。

希望有成功经验的人留个言,看看我的操作哪里有问题~

Logic Analyzer 逻辑分析仪,对于FPGA开发人员来说,是不可或缺的工具,当代码能够综合、实现,但是烧写之后出现问题或者不能达到想要的效果,那么就需要debug,logic analyzer就是debug过程中提高工作效率的利器。如果不实用logic analyzer抓取内部信号,就只能陷入“修改代码à查看现象à再次修改代码à再次查看现象……”的循环,相反使用logic analyzer可以快速定位问题。因此logic analyzer的易用性也是衡量IDE的指标之一。

首先,大概回顾一下ISE、XPS、PlanAhead是如何使用ChipScope的。

ISE:

step1:添加ChipScope IP(cdc文件),可以自己命名,此处假设命名为ChipScope.cdc

step2:双击所添加的ChipScope.cdc,进入Core Insert界面,设置采样深度、触发信号、添加想要抓取的信号、指定时钟,保存,退出。

综合、实现、生成比特流,配置FPGA之后,在ISE主界面双击Analyze Design using Chipscope,进入结果获取窗口,设置触发条件后,就可抓取信号了。

XPS和ISE类似,添加ILA core的菜单位置不太一样,由于ChipScope并没有被集成进ISE,所以结果窗口是一样的。

PA用的不多,PA算是ISE和Vivado的过渡产物,就使用而言PA的很多操作和Vivado是类似的,但是PA并没有对所有工具进行集成,只是用一个和Vivado类似的界面去调用各个流程所需要用的工具。PA下Logic Analyzer的使用和Vivado也是类似的,如果没记错的话。

就我个人的使用感受而言,XPS中添加的ILA core触发条件无法设为R(上升沿触发)、F(下降沿触发),不知道是不支持还是我没有找到设置方法。两者相比较而言,ISE下ChipScope的使用更加得心应手。

Vivado将逻辑分析仪进行集成,貌似还没有起名字,暂时叫LA吧。添加想要抓取的信号较ISE而言更为方便,大多数信号都不需要手动“make connection”,IP核设置界面(Set Up Debug向导进入)和结果获取界面(入口在Hardware Manager)仍然是分开的。

不论是ISE的ChipScope还是Vivado的LA,在易用性方面都不及SignalTap,客观的说SignalTap要比Xilinx的LA好用很多、方便快捷——信号设置和结果查看在同一个窗口完成,触发条件也是一目了然,新增加信号只需一个简单的双击即可弹出信号检索窗口。

好了,比较完了,该用还得用,所以还得学。

这里,以《Vivado实战——节奏灯》的工程为例,研究如何使用logic analyzer。

1、 打开所建立的工程

在新建工程的过程中就可以添加logic analyzer IP,把自己感兴趣的信号连接至IP。再一种是未能满足设计要求,再回过头来添加analyzer,进行debug。两种差别不大,都是在功能设计完之后再添加debug需要查看的信号。

2、 添加信号

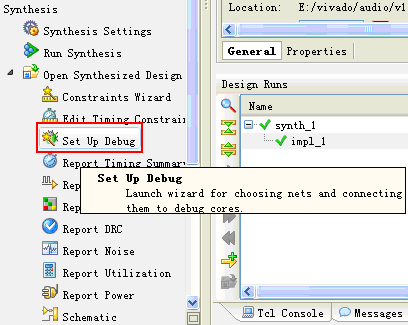

图1 set up debug

如图1所示,在最左侧的Flow Navigator子窗体,找到Open Synthesized Design,展开,点击Set Up Debug菜单,进度条跑完之后进入向导界面,如图2所示。

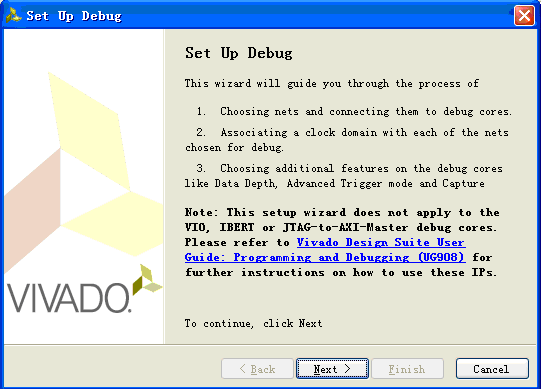

图2 set up debug向导

点击Next按钮,进入nets添加、删除界面,如图3所示。

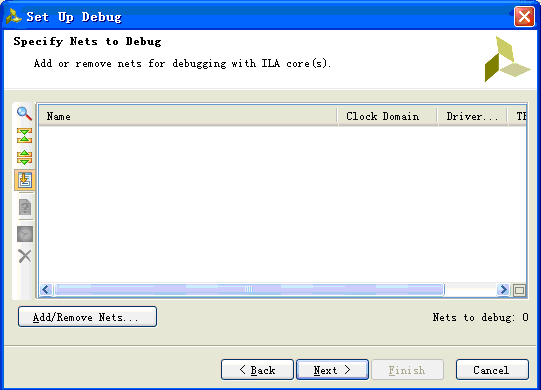

图3 add/remove nets

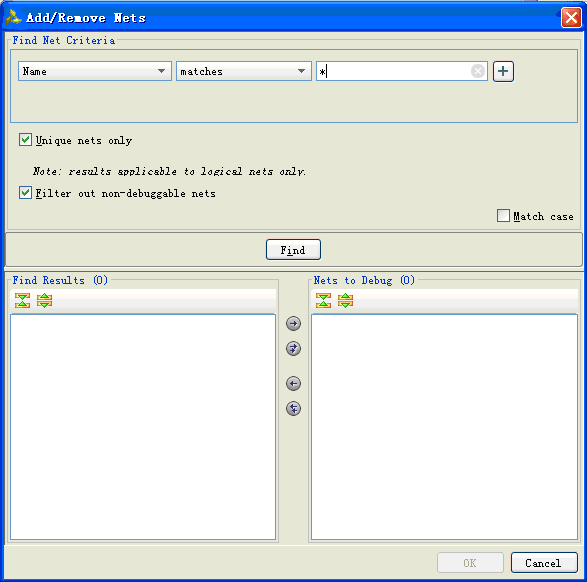

点击Add/Remove Nets按钮,进入下一界面,如图4所示。

图4

nets添加完毕,如图5所示。

图5 nets添加完毕

点击OK,进入下一步,如图6所示。

图6 nets添加完毕,返回

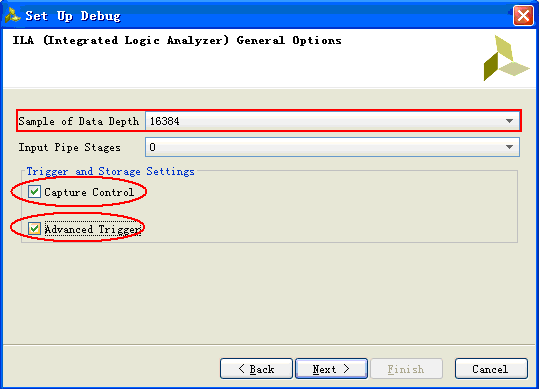

直接NEXT,进入下一界面,图7所示。

图7 采样深度

设置采样深度,选择capture control、advanced trigger,高级选项都选上,分析时比较方便。

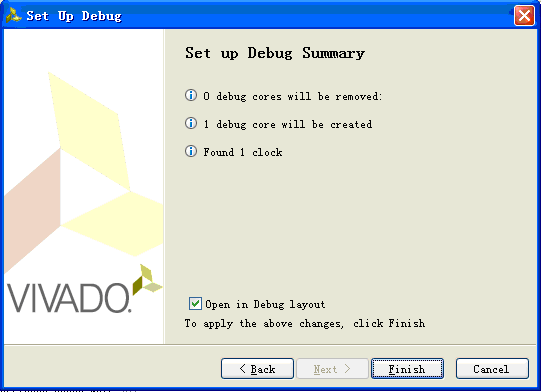

设置完毕后点击Next,进入summary界面。

图8 summary

点击Finish,设置完毕。

3、 添加了新的IP,需要重新实现

首先保存,然后重新Generate Bitstream。Vivado会提示需要重新Implement,点击OK,重新实现。

4、 抓取信号,分析结果

4.1、打开logic analyzer

Flow Navigato > Program and Debug > Open Hardware Manager,如图9所示。

图9

选择Open New Target,按照向导一步一步Next,在XP下,接下来就进行不下去了……

WIN7也差不多到头了,向导运行完毕,但是通信链接建立不上……

问题是,同样的操作,同样的工程,在前一阵子还是没问题的,逻辑分析仪能够跑起来……

这个LA真是搞的我吐血了,回想前一段时间用SignalTap,那叫一个舒服,现在——都是眼泪啊!

版权声明:

本文由博主“cuter”发布。欢迎转载,但不得擅自更改博文内容,也不得用于任何盈利目的。转载时不得删除作者简介和版权声明。如有盗用而不说明出处引起的版权纠纷,由盗用者自负。

博客官方地址:

ChinaAET:http://blog.chinaaet.com/cuter521