【原创】Vivado HLS是如何快速把C/C++算法导入System Generator模型的

0赞Vivado HLS(high level synthesis)可以直接把现有的C/C++算法转换为RTL,而System Generator则可以把现有的基于Matlab/Simulink模型实现的DSP算法直接转换为RTL,二者的侧重点不同,但是也可以有一定的交集。那二者直接如何不通过Vivado IDE而直接进行互动呢? System Generator中自带了名为“Vivado HLS”的模块,可以方便我们直接把Vivado HLS中调试好的C/C++算法导入到Simulink中去。下面我们就来看看这个方法是如何实现的。

首先,打开Vivado HLS软件,然后点击菜单栏上的File---New Project,如图1所示。

图1 新建Vivado HLS工程

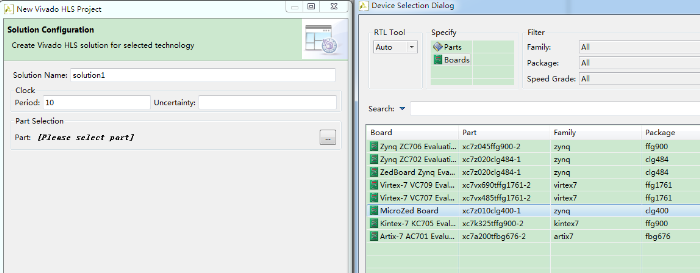

点击Next,然后输入项目工程,暂时先不指定和添加源程序,在提示选择器件类型时选择开发板MicroZed,如图2所示。然后点击Finish就完成了Vivado HLS工程的创建。

图2 选择Vivado HLS使用的开发板

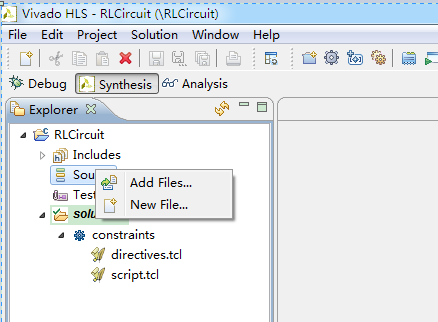

进入Vivado HLS主界面之后,在工程浏览器的Source上点击右键,选择新建源程序,如图3所示。

图3 新建源程序

在这里我们新建一个名为RLcircuit.cpp的源程序和名为RLcircuit.h的头文件,它们代表的是一个RL电路的传递函数:

程序则是该传递函数的离散化。源程序为:

#include "RLcircuit.h"

dint RLcircuit(dint x)

{

static dint yz=0;

static dint xz=0;

static dint y;

y=yz*dint(0.9999)+xz*dint(0.00005)+x*dint(0.00005); //fixed_32_28

xz=x;

yz=y;

return y;

}

头文件为:

#ifndef _RLCIRCUIT_H_

#define _RLCIRCUIT_H_

#include <stdio.h>

#include "RLcircuit.h"

#include "ap_fixed.h"

typedef ap_fixed<32,4, AP_RND, AP_SAT> dint;

dint RLcircuit(dint x);

#endif

需要注意的是,上面的源程序中,x1,y1和y要声明为函数内的静态局部变量,否则在C综合时,端口x会被优化掉而使得整个程序都被优化掉。由此也可以看出,良好的编程习惯对正确实现Vivado HLS的高层次综合也有着重要的意义。

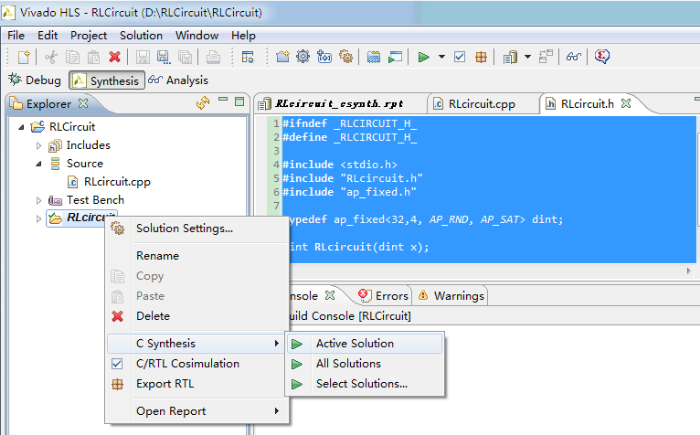

程序输入完成之后,可以进行对C/C++代码的综合了。在Vivado项目管理器中的Solution上点击右键,选择C Synthesis,如图4所示。

图4 运行C代码的高层次综合

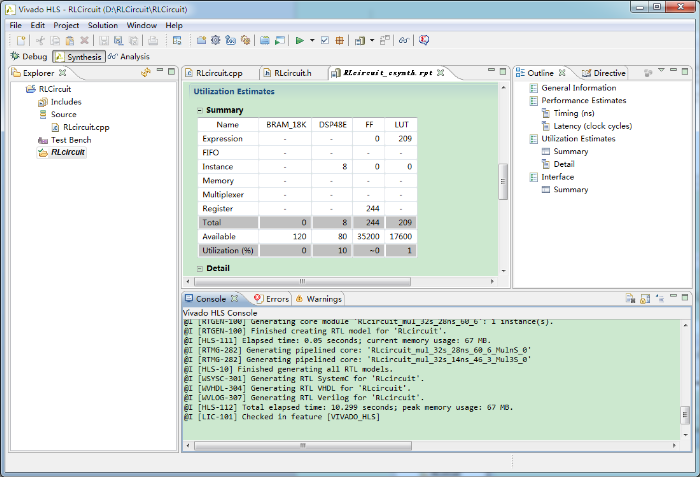

如果有错误,比如某个变量未定义之类的,Vivado HLS会提示我们详细的错误信息;在没有错误之后,Vivado HLS很快就完成了C代码的综合过程,如图5所示。

图5 C代码综合完成的提示

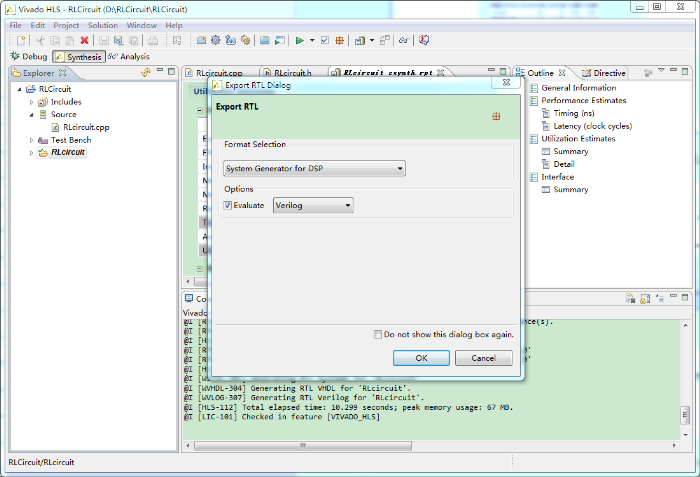

然后我们便可以将综合之后的代码生成RTL了。在图5中对应的右键菜单上选择Export RTL,并选择导出到System Generator如图6所示。

图6 Vivado综合结果导出到System Generator

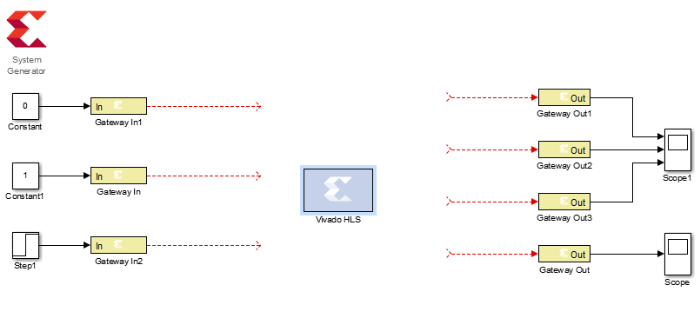

接下来,我们便可以在System Generator中测试Vivado HLS生成的RTL了,在System Generator中新建模型如图7所示。

图7 新建System Generator模型

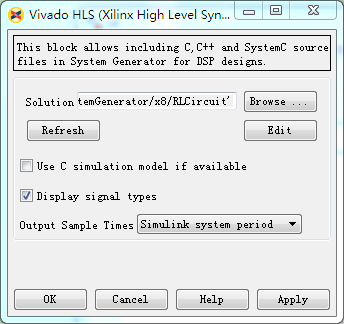

由图7可见,Vivado HLS模块在没有配置之前是无法连线的,因为模型还不知道它的端口信息。所以接下来我们双击Vivado HLS模块,把前面完成综合的模型信息填进去,如图8所示。

图8 配置Vivado HLS模块

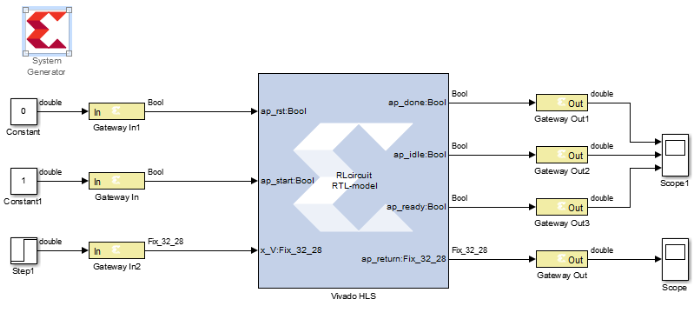

搭建完成之后的模型如图9所示。

图9 搭建完成的含有Vivado HLS导出结果的模型

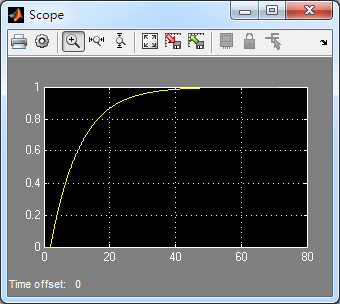

这里给定的输入是一个阶跃信号。然后运行仿真,我们搭建的一阶RL电路的阶跃响应便得到了,如图10所示。

图10 含有Vivado HLS导出结果的模型的仿真结果

接下来,可以在模型的集成上加入更多的DSP算法,然后一起导出为RTL了,例如导出到Vivado里面做为一个IP。

谢谢大家!![]()