Vivado利器优势之我鉴-------时序

1赞在所做设计的功能仿真通过之后,下一步就是验证其是否达到了理想的频率,就是我们所关心的时序问题。对于有经验的设计者来说,在整体设计和编写代码时就会考虑到时序的问题,对整体设计和代码进行优化,所以时序问题最后往往也不会成为问题。然而,对于新手来说,或者当所做的工程项目较大时,时序问题往往成为棘手的问题,一套强大的时序分析工具对设计者来说显得尤为重要。

Vivado提供了一套完整的时序分析工具,可以方便快速地帮助用户分析时序中的问题,进而针对其进行改进。虽然在ISE、Quartus等开发套件中也都有时序分析的工具,然而个人觉得Vivado在时序分析这块下了不少的功夫,具有更强大的功能和更友好的用户界面,不仅利于新手上手使用,而且也让老手用起来得心应手。结合我一年多来在Vivado中调时序的经验,跟大家分享以下使用体验和感受。

在开发流程中,可以对综合之后或者实现之后的设计进行时序分析,下面以实现之后的时序分析为例来说明。首先要打开实现设计,将所做设计实现后的文件载入到内存中,如下图:

一、 分析全面,功能强大

如下图,时序分析主要有以下几方面:检查时序、报告时序、报告时序总结、报告脉冲宽度、创建余量柱状图、报告时钟交互、报告数据表格以及重置时序。我们经常用到的是其中的3、5、6功能部分,Report Timing Summary对设计做一个整体的时序分析,供设计者了解各个方面时序的概况;Create Slack Histogram罗列出设计中每条路径的时序情况,供设计者做具体的分析;Report Clock Interaction分析跨时钟域信号的时序情况,供设计者较好地掌握跨时钟域的设计部分。

Vivado中不仅有着丰富的分析功能,而且也可以让设计者针对自己的分析需求对每个分析功能做设置,如下图中Report Timing Summary中的设置,包括路径延迟类型、边角延迟类型、路径显示等,用户使用起来更加得心应手,根据自己的需求来分析查看。

另外有两点值得我们注意:1)Vivado中的时序分析不再具体给出系统主时钟的最高运行频率,而是以时序约束为导向来分析每条路径的时序余量;2)对于跨时钟域的信号,如果没有约束其不相关,Vivado默认其相关,这个与ISE中的认识相反。

与ISE中的时序分析相对比,我们会发现Vivado的时序分析功能更加强大,分析的更加全面。

二、 界面友好,使用方便

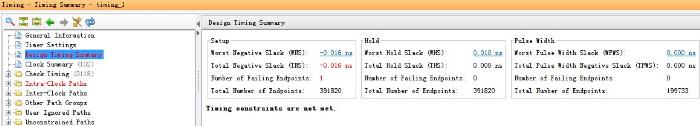

另外值得称赞的是Vivado中时序分析结果显示的界面更加友好,与软件界面的整体风格融为一体,便于查看和分析。如下图Timing Summary的显示界面,各窗口分割清晰,采用树状显示结构,对有问题的部分用红色显示标出,整体情况一目了然。

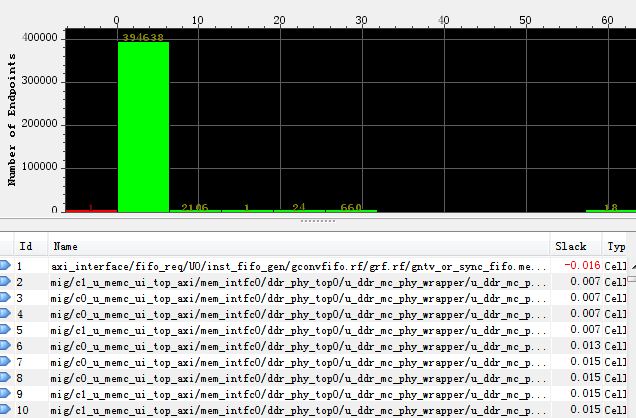

下图Slack Histogram的窗口,不仅有图形化的界面,统计分析更为直观,而且各路径时序余量显示也更加整洁,便于分析查找。

相对于ISE中的时序界面,用户很明显感受到Vivado中的更为友好,使用起来也方便了不少。美中不足的一点是Vivado载入内存的东西较多,对内存的需求较大,所以在使用时会有一点点的卡机现象。

三、多视角相互配合,分析更准确

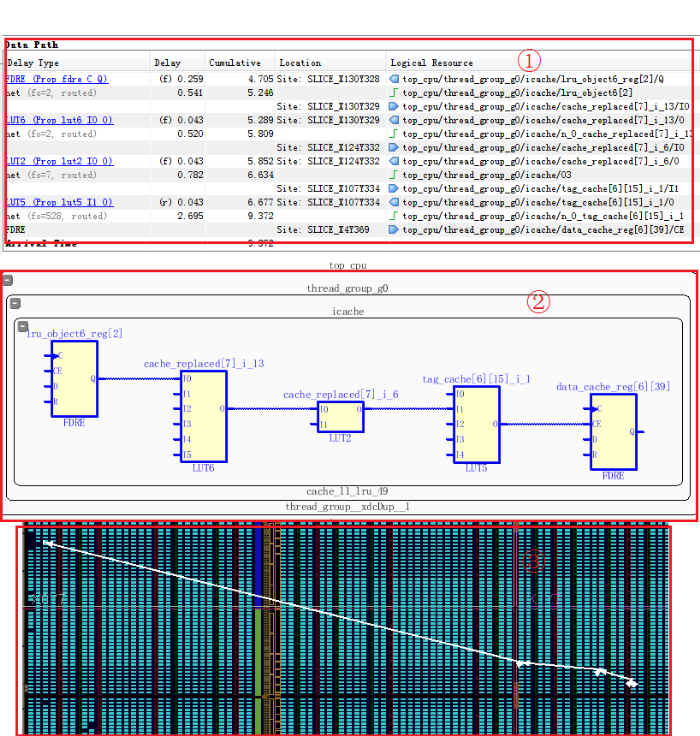

在对整体的时序情况有所把握之后,接下来就要对每条不满足时序的路径做具体的分析了。由于Vivado是个集大成的开发环境,我们可以借助多个窗口的视角来对问题路径做准确的分析,举个例子,对于其中一条不满足时序的路径,我们首先分析其路径时序,如下图中的图①,分析该路径的逻辑级数以及每级逻辑的门延迟和线延迟,定位消耗时间较大的部分。然后,借助图②中的电路,将问题路径还原到所写的代码中,分析问题在哪个模块中的哪段代码中。最后,查看芯片布局布线图,即下图图③,进一步分析问题路径的布局布线情况,准确定位问题原因,如整体设计不合理导致布线紧张、代码书写不合理导致综合较差等等原因。

多视角的分析结果便于用户从各个角度来审视问题,准确定位原因,给后续的改进工作提供正确的方向。

由于笔者的开发经验不足,博文中可能存在一些认识上的错误,希望大家多多指正![]() 同时,也希望大家多多支持,你们的肯定是我努力的动力

同时,也希望大家多多支持,你们的肯定是我努力的动力![]()