Vivado Logic Analyzer的VIO

0赞

本文基于Vivado 2014.2

ChipScope有两种使用的方式:cdc和IP Core。由于VIO的IP只能通过IP的方式来使用,所以IP的方式ChipScope中有重要的意义。

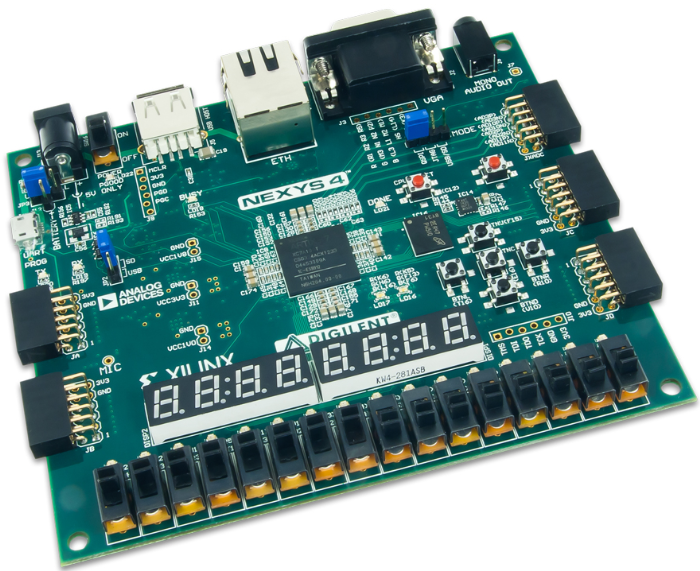

同样,Vivado中的VIO也只能通过IP的方式来使用。本文使用Digilent的Nexys-4板卡来探讨VIO的使用。关于Nexys-4的信息,请参考http://www.digilentchina.com/product-more.asp?ClassId=1&Unid=306

在设计中添加16个LED和16个开关的端口,并连接到VIO中去。生成bit文件后下载到板子上,在Hardware Manager中额可以看到VIO的控制界面。

在Debug Probes中可以看到,这个设计包含了一个ILA和一个VIO的IP。

在VIO的控制界面中,可以看到所有连接到VIO的端口,分为输入和输出两个部分。

首先看输出,将16个LED调整为按键模式,然后如上图所示将部分信号置为高电平。

可以看到相对应的LED被点亮。

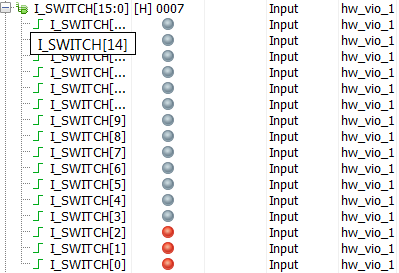

下面是input,将部分开关置为高电平,并观察VIO界面中的输入部分。

可以看到相关的信号已经被置为高电平。

在ChipScope中,ICON是一个重要的IP,IP例化ILA和VIO的时候,都需要通过ICON。

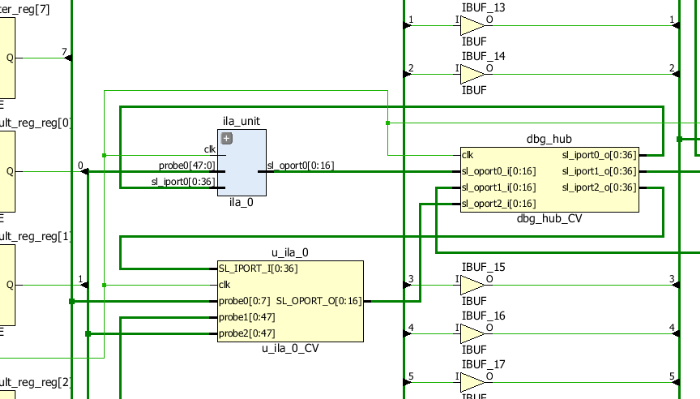

通过对ICON的调用,可以很好的利用JTAG来连接ILA和VIO。但是,在Vivdao中,这个IP被去掉了,取而代之的是Vivado自动添加的dbg_hub。这样就不能很好地控制JTAG的BSCAN,这可以说是Vivado的一个很大的损失。

不过,既然dbg_hub是自动添加的。那么理论上,对ILA和VIO端口的识别也是自动的。ChipScope中需要手动添加ICON,导致两种使用ChipScope的方式无法共存,尤其是在使用VIO的时候,无法使用cdc文件。在Vivado中,是否可以共存呢?

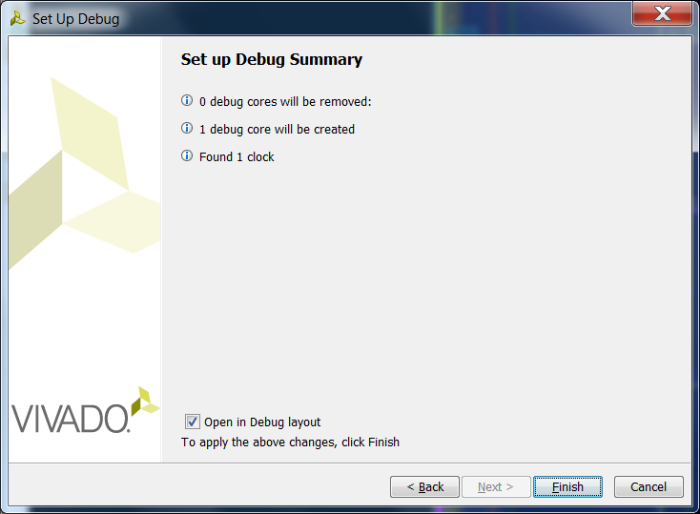

在已经添加ILA和VIO IP的设计中,打开综合结果,找到相关的信号,设置debug标示。然后在Set Up Debug中可以发现,被连接到ILA IP和VIO IP的信号可以一并被识别出来。修改后如下图所示设置完成之后,发现界面提示生成了一个debug的core,即一个ILA。

从布局布线的结果来看,Vivado在ILA和VIO IP的基础上,又增加了一个ILA。

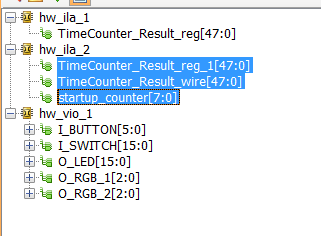

同时,打开Debug Probes,可以看到两个ILA存在于设计中。

可以看到,由于Vivado可以自动添加dbg_hub,所以可以让工具自动连接相关的IP,让两种使用Vivado Logic Analyzer的方法可以混合使用。这极大的方便了VIO的使用。

虽然Vivado确实了ICON,无法对JTAG BSCAN进行更多的控制,对于一些高级使用有些不便,但自动的dbg_hub功能确实方便了使用,应该算是一个进步。