PWM 任意频率 任意占空比 - LM3401

0赞

发表于 2015/5/15 10:00:39

阅读(4182)

一、硬件架构

光源控制芯片LM3401,是美国国家半导体公司 National Semiconductor的产品,其典型特点:

1、 2.8A Typical Switch Current

2、High Switching Frequency

— 525 KHz (LM3410-Y)

— 1.6 MHz (LM3410-X)

3、Current-Mode, PWM Operation

4、Input voltage range of 2.7V to 5.5V

Output voltage range of 3V to 24V

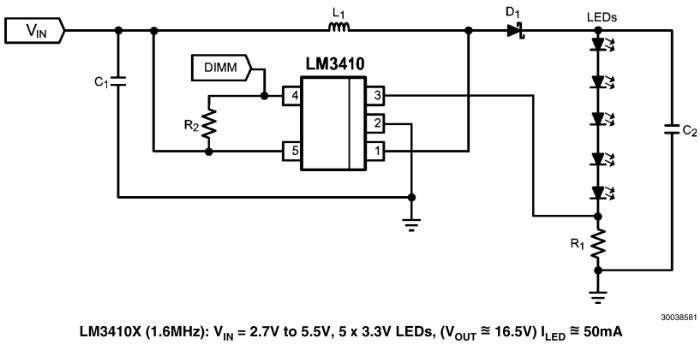

1.1 典型应用电路

一个芯片可以驱动5个高亮LED,并且典型电流为50mA

1.2 控制输出为FPGA 任意一款FPGA均能搞定此功能

二、代码设计

代码功能:输出任意PWM频率,及占空比

代码如下:

verilog:

module led_PWM

(

input clk_ref,

input sys_rst_n,

output led_pwm

);

//-------------------------------------------------------------------------

//contrl led -PWM div

parameter PWM_FREQ = 20'd10000; // pwm frequency: 20'd10000 10KHz (Even the div frequency)525k 1.6m

reg [19:0] cnt_pwm;

always@(posedge clk_ref or negedge sys_rst_n)

begin

if(!sys_rst_n)

cnt_pwm <= 20'd0;

else if(cnt_pwm < PWM_FREQ - 1'b1) // pwm frequency:

cnt_pwm <= cnt_pwm + 1'b1;

else

cnt_pwm <= 20'd0;

end

//reg [19:0]Duty_ratio = 20'd3000; //pwm Duty ratio: Duty_ratio/PWM_FRE

//wire [19:0] Duty_ratio;

parameter Duty_ratio = 20'd9800;

//触发器输出

//reg clk_pwm_r1;

//always@(posedge clk_ref or negedge sys_rst_n)

//begin

// if(!sys_rst_n)

// clk_pwm_r1 <= 1'b0;

// else

// clk_pwm_r1 =((cnt_pwm >= 0) && (cnt_pwm < Duty_ratio))? 1'b1 : 1'b0;

//end

//组合逻辑输出

wire clk_pwm_r1 =((cnt_pwm >= 0) && (cnt_pwm < Duty_ratio))? 1'b1 : 1'b0;

assign led_pwm = clk_pwm_r1; //clk_pwm

endmodule

控制 PWM_FREQ 调节PWM 频率,控制Duty_ratio 调节PWM 占空比。LM3401 PWM频率范围:1 Hz to 25 kHz。

~1MNEL[IY.png)

testbench:

`timescale 1 ns/ 1 ns

module led_PWM_vlg_tst();

reg clk_ref;

reg sys_rst_n;

// wires

wire led_pwm;

// assign statements (if any)

led_PWM i1 (

// port map - connection between master ports and signals/registers

.clk_ref(clk_ref),

.led_pwm(led_pwm),

.sys_rst_n(sys_rst_n)

);

initial

begin

clk_ref=0;

forever #5 clk_ref = ~clk_ref;

end

initial

begin

sys_rst_n=0;

#100;

sys_rst_n=1;

#1000;

$top;

end

endmodule

波形图:

既然选择了,便不顾风雨兼程。。。