BASYS3 开发板指导(3-8译码器)

1赞BASYS3 开发板指导

(通过使用Vivado 2015.1设计解码器)

提示:你将需要安装Vivado Webpack在电脑上(或者其他版本)。

这个指导将会展示如何生成一个简单组合的设计(一个3-8译码器通过拨码开关和leds),可以在Basys3开发板上实现。

启动Vivados设计软件

选择生成新的工程

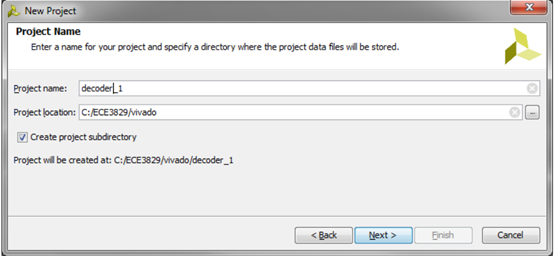

点击Next然后为你的工程输入一个名字和存储的位置:

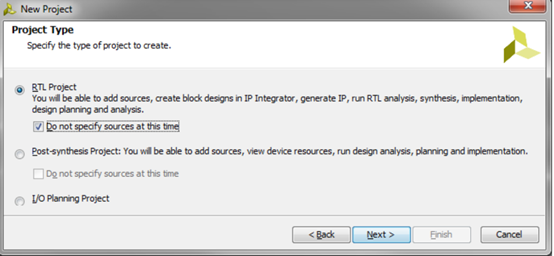

点击Next和选择RTL工程类型:

勾选“Do not specify sources at this time“,点击next。(此时不需要指定源文件)

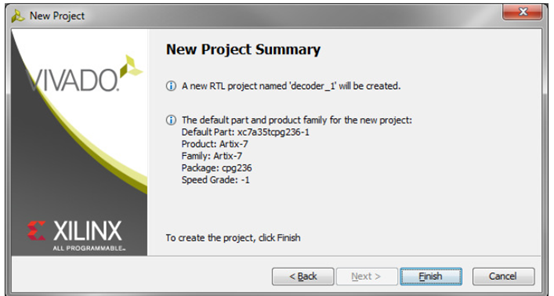

选择正确的Xilinx FPGA型号,Basys3开发板的是XC7A35T-1CPG236C

点击Next,然后点击Finsh:

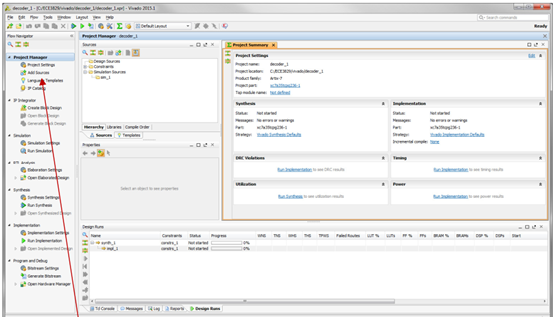

打开工程窗口

我们现在需要添加一个Verilog的设计源文件去描述我们的译码器操作。

点击左侧的Projiect Manager窗口Add Sources(或者选择菜单栏的File=>Add Sources):

选择Next

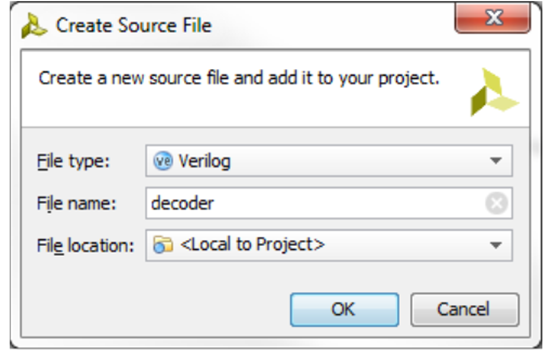

然后选择生成文件(点击“+”的按钮)同时输入文件名 decoder:

然后点击OK和Finsh

我们现在可以指定inputs和outputs去生成3-8译码器(我们将会使用三个拨码开关和8个leds)

点击OK

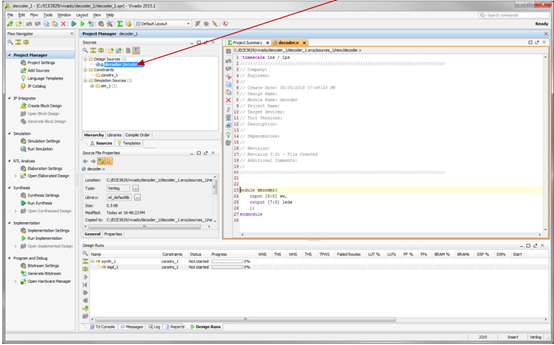

返回Project Manager Sources的窗口,双击刚新建的decoder.v的文件,然后你将会看到verilog的文件出现在右边的窗口里:

你可以添加你的项目名字和文件的描述在顶头的描述信息里。

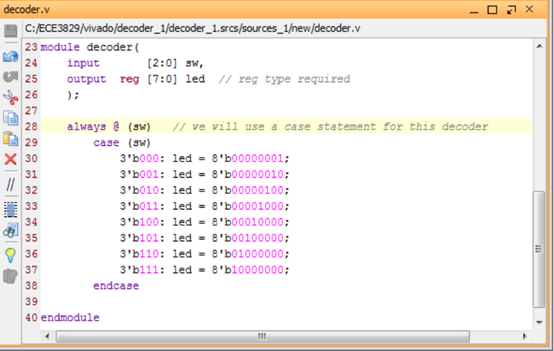

我们可以添加verilog的语法去描述我们3-8译码器。

有许多的方法可以去设计译码器,这是其中一个使用case的例子。

现在我们可以综合设计。

点击Project Manager window中的 Run Synthesis选项。

经过综合完成后应该没有错误或者警告。

如果你打开综合设计你可以看到资源的使用描述(可以看到很大一部分都是空的,因为我们的简单设计只用到了FPGA资源里面很小的一部分):

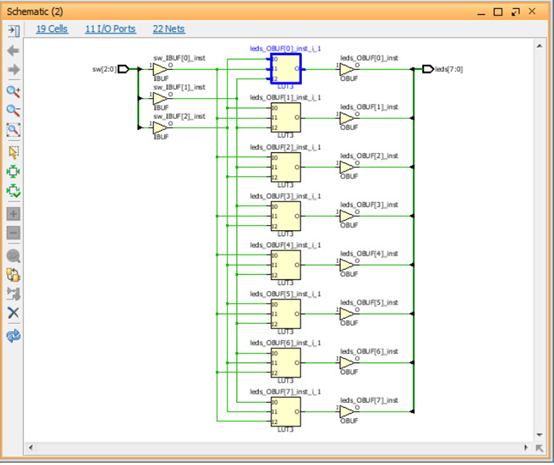

但是你也可以查看原理图描述,看到被使用的输入输出缓存:

在实现之前我们需要指定FPGA使用过的SW和LED的引脚。

看Basys3 的原理图去选择FPGA的管脚。

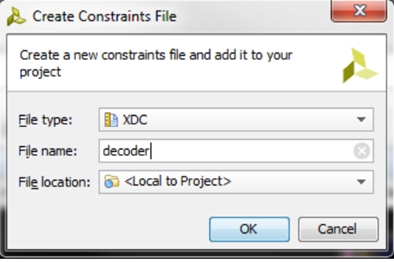

然后点击Add Sources and 选择‘Add or create constraints’:

命名为decoder

在源文件的窗口点击Constraints =>constrs_1 => decoder.xdc来打开文件,我们可以添加约束给所有的输入输出信号。(你也可以下载一份Basys的XDC约束文件在Digilent的官网上,只需要复制相应的管脚到你的设计中就可以)

这些约束指定管脚的信号和电平描述。

现在我们已经正确配置了设计中使用的管脚,现在我们可以实现设计了。

点击Project Manager window中的Run Implementation。

你将会在实现后找到两条警告,因为我们的设计没有指定任何的时序约束,对于这个简单的设计我们可以忽略这些警告。

现在我们可以生成比特流文件,点击Project Manager窗口上的 Generate Bitstream

下一步就是下载比特流文件到FPGA.

在Basys3开发板上我们要明确JP1是设置在JATA模式下,USB连接开发板然后打开电源。

在Project Manager 下选择 Hardware Manager ,点击Open Target ,然后 Auto

Connect

你应该看到Xilinx xc7a35t_0出现在Hardware Window窗口里:

点击Program Device然后选择decoder.bit(文件自动加载):

然后选择下载(忽略那些有关漏掉的调试警告和违反规则)

下载过程需要几秒然后Basys3的开发板上Done的led会点亮。

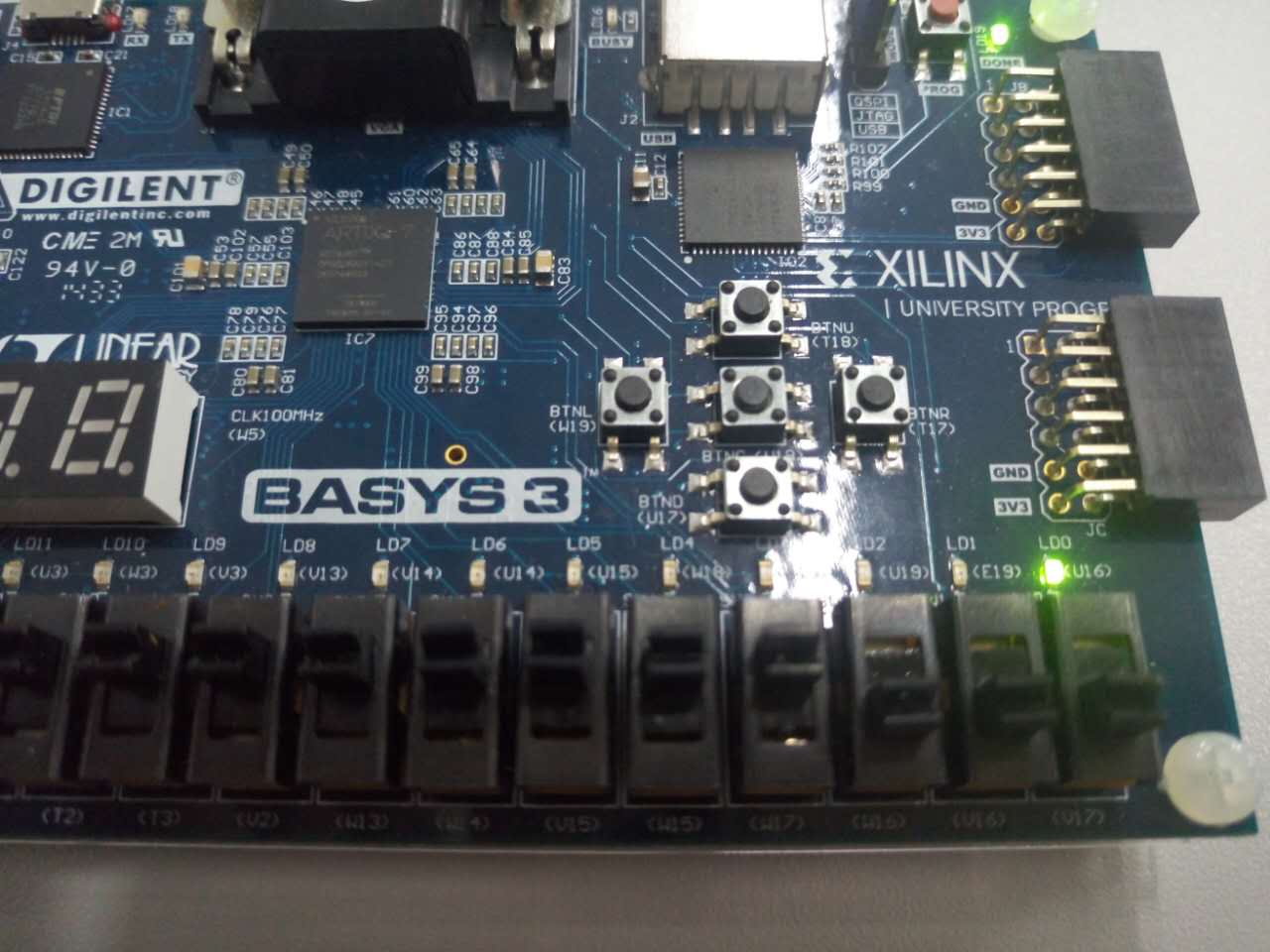

你就可以发现你的解码器已经在FPGA上实现了

改变三个拨码开关(SW2,SW1,SW0)通过所有的8种组合来验证led的点亮和熄灭。

祝贺你!

你已经通过一个设计完成了综合,实现,下载比特流文件,虽然这只是一个简单的例子,但是任何的设计都是在基于这些基本的步骤实现的。

关闭Hardware manager返回到Project Manager的窗口

下载串行闪存

FPGA 是个易失性的器件,所以比特流文件在开发板断电后不会保存,重新上电之后也读不到之前的bit的文件。我们可以通过QSPI串行烧写bit的文件到开发板上,这样重新上电就会从flash中读bit文件了。

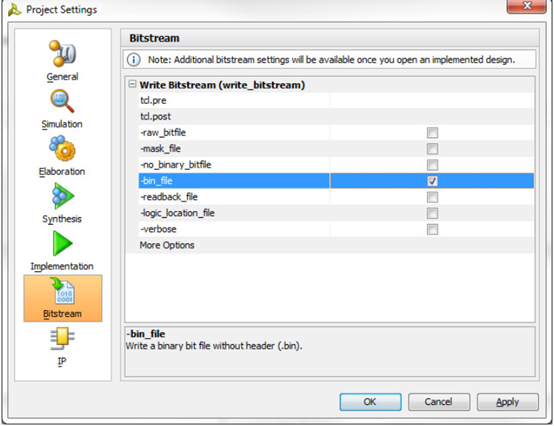

在Project manager里点击Program and Debug中的Bitstream Settings

勾选bin_file的选项

点击ok

点击Generate Bitstream生成比特流文件

生成之后,你可以在文件夹decoder_1 => decoder_1.runs => impl_1 directory中看到decoder.bit 和decoder.bin这两个文件

在Hardware Manager窗口,右键点击FPGA选择Add Configuration Memory Device:

选择Basys3开发板上的串行Flash的芯片型号

选择Spansion这个制造商,然后选择32Mb的大小

点击ok

点击ok,

选择decoder.bin的文件

点击ok,

提示:这会擦出之前存在的QSPI flash

QSPI flash会被擦除,然后下载decoder.bin文件

曾经烧写过话,需要断电之后改变JP1的跳线帽从JATA 模式转换到QSPI 模式

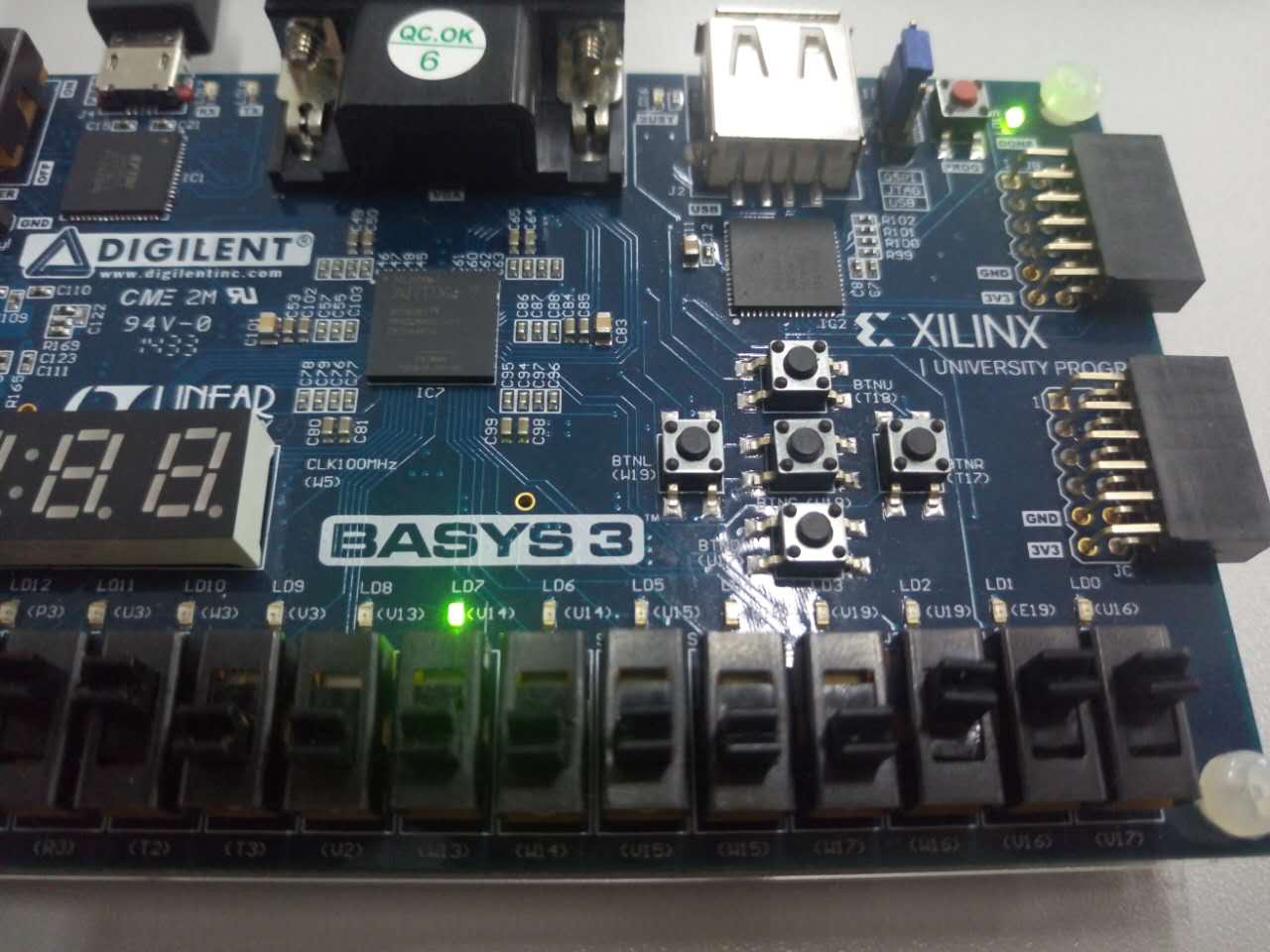

开发板供电的led灯亮起的时候就表明decoder的设计文件自动从flash加载到FPGA中,你可以通过滑动拨码开关来观察led的变化情况。

学习心得

先上开发板看看结果

当拨码开关为 000 状态时,led0点亮

当拨码开关为 010 状态时,led2点亮

当拨码开关为 111 状态时,led7亮

第一次写博客,心情有少些激动,虽然内容比较简单,但是自己还是用心去做了,一步一步翻译下来,接着在软件上操作,到硬件的实现,过程学到不少的东西,总体上知道如何实现一些简单的设计,听说FPGA最难的就是时序设计,当然这个设计中没有,所以想在接下来的学习中打好基础,努力想各位大神学习,提高自己 。

。

下面有附件(⊙o⊙)哦

BASYS3 开发板指导文件(有英文原版,菜鸟中文翻译的不好多多指导 )。

)。

基于vivado2014.4的decoder的工程文件。