Vivado利器优势之我鉴-------集大成

0赞在ISE套件中,有ISE、PlanAhead、XPS、SYSTEM GENERATOR和Chipscope等,这些软件都有着自己独立的入口,负责工程开发中的不同环节。软件接口之间的松耦合使得设计者需要来单独调用这些软件,这样不仅带来使用上的不便,而且也给工程文件的管理带来不便。

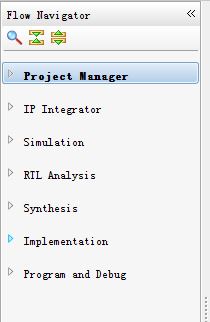

Vivado是一个集成度较高的开发环境,集ISE套件中各种软件的功能于一体,建立各个工具之间紧耦合的接口。集大成的开发环境不仅有着便于用户使用的统一的用户界面,而且可以使得设计流程一体化。下面我们就随着使用Vivado开发一个工程的流程,来看看Vivado所集成的开发工具:

上图是Vivado开发的流程导航,贯穿工程开发的每一个环节,提供了开发所需的所有工具。该流程导航位于软件的左侧,方便用户使用。

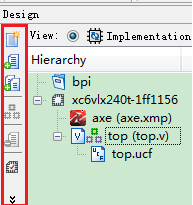

1. Progect Manager

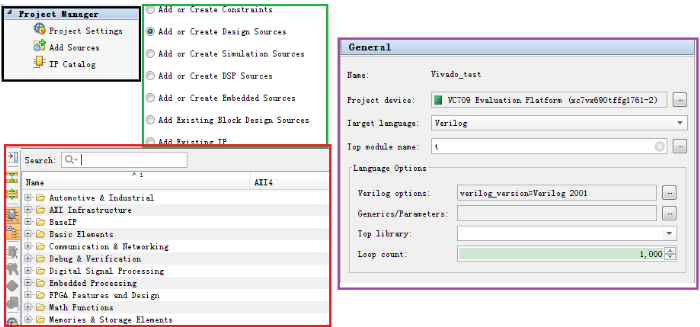

如上图所示,Progect Manager负责工程的设置、添加文件以及IP核,能够很好的组织和管理工程中的文件和IP。相对于下图ISE中文件的添加和管理,Vivado显得更为方便和有条理。

2. IP Integrator

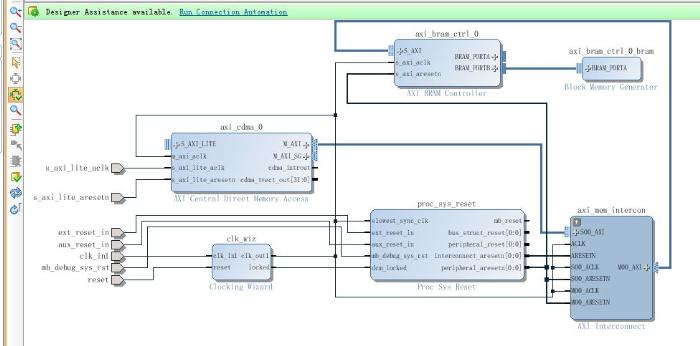

如上图,IP Integrator(IP集成)负责创建、打开以及生成块设计,能够将多个IP集成在一起构成一个更大功能更多的IP或者系统。下图是IP Integrator的一个实用例子,在设计块中加入多个所需的IP,首先分别设定每个IP的参数,然后将其连接起来,最后封装外部接口。

我认为IP Integrator具有ISE套件中XPS的功能,XPS是将多个IP组成一个系统,并最终将其综合实现。两者只是用户界面不同,个人觉得Vivado的界面使用起来更为方便和人性化。

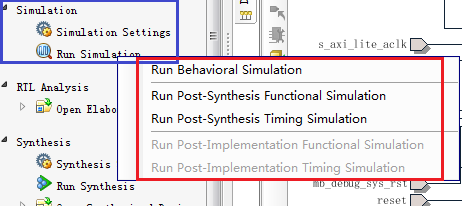

3. Simulation

仿真的部分包括仿真参数的设定和跑仿真。如上图的红框所示,有5中类型的仿真,包括行为仿真、综合后功能仿真、综合后时序仿真、实现后功能仿真以及实现后时序仿真,可以在工程开发的不同阶段来做,验证程序的正确性。

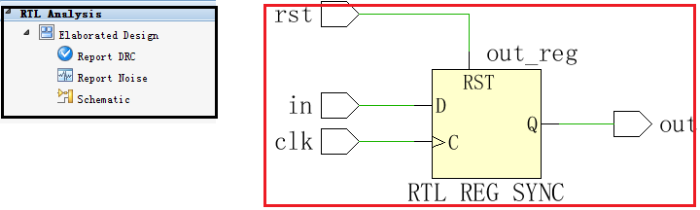

4. RTL Analysis

上图是RTL分析的流程,包括DRC检查、Noise分析以及电路图。图右边红框是工程中某一部分代码综合出来的电路图,我们可以分析改电路图来检查所写的代码是否被编译器正确理解。

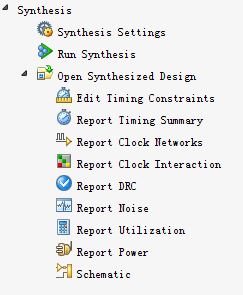

5. Synthesis

上图是综合部分的工具,包括综合参数的设置、跑综合以及打开综合设计。在综合设计中包括了很多多综合后的分析,包括时序、资源利用、功耗等等,使用这些工具我们可以详细了解我们所设计和编写的代码在综合这一步的情况,以此来确定是否满足设计需求。

6. Implementation

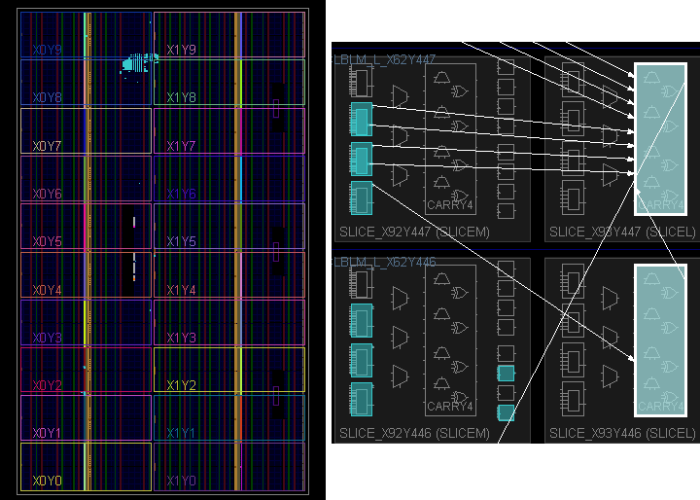

上图是实现部分的工具,与综合部分有很大的相似,可以对工程做最后的分析和检查。同时,值得注意的是,在打开实现设计时,会将实现后的设计映射到所用的FPGA芯片上,如下图,具有ISE套件中的PlanAhead,方便用户分析和修改。

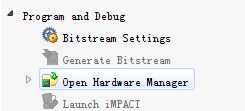

7. Program and Debug

最后一步就是生成bit文件和上板子调试了,如上图,包括bit文件参数的设定、生成bit文件、打开硬件管理以及调用IMPACT等几部分。其中,Hardware Manager可以下载bit文件至FPGA,也可以通过一些调试IP核来抓取和输入分析信号,具有Chipscope的功能,但其集成在开发流程中,使用起来更为简单和方便,我也会将在后续的博文中通过实际的例程对其优势做详细的分析。

由于笔者的开发经验不足,博文中可能存在一些认识上的错误,希望大家多多指正![]() 同时,也希望大家多多支持,你们的肯定是我努力的动力

同时,也希望大家多多支持,你们的肯定是我努力的动力![]()