Vivado利器优势之我鉴-------hardware manager

0赞Hardware Manager是集成在VIVADO中的片上调试工具,功能类似于ISE套件中的Chipscope,但功能更加强大,且使用更加方便。Hardware Manager不仅能够管理本机或者远程连接的FPGA资源,将生成的bit文件下载,而且也可以对片上逻辑进行调试,Hardware Manager将片上调试的工作和文件集中在该工程的目录下,使得软硬件调试结合的更加紧密。

在实际的工程项目中,使用Hardware Manager进行片上调试给我们的工作带来了极大的便利,我也确实感受到Hardware Manager的强大,所以一直以来想写一篇关于它的博文来与大家分享。但鉴于我能力有限,所以只能从比较浅的表面来介绍Hardware Manager及其使用,希望能抛砖引玉,激起大家摸索Hardware Manager的兴趣。

一、 调试IP核

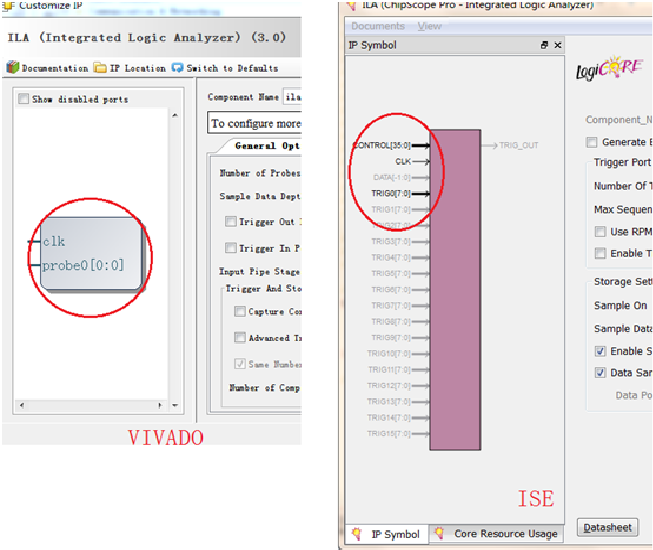

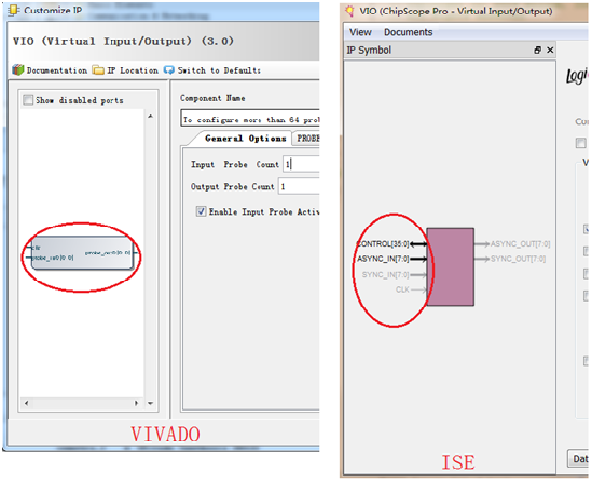

同Chipscope的调试原理一样,Hardware Manager也是借助于Jtag来实现的,也需要在工程中加入调试IP核。然而,对比ISE中和VIVADO中的调试IP核,我们会发现,VIVADO中的调试IP使用起来更为方便。首先,使用Chipscope时需要用到ICON、ILA或VIO来配合工作,而在Hardware Manager下进行了简化只需要用到ILA或VIO即可,ICON不需要用户来显式控制。

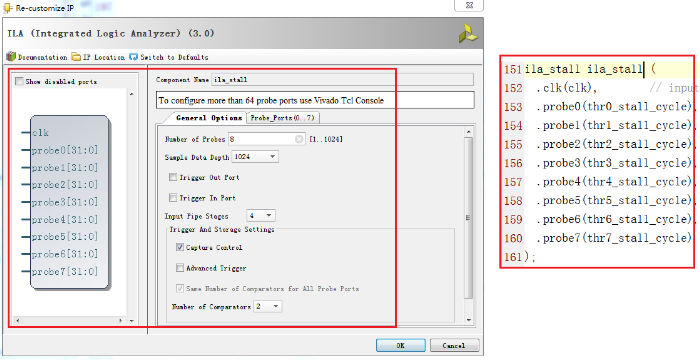

其次,如上图是VIVADO和ISE中ILA调试IP的对比,从引脚来看VIVADO中ILA的引脚分类更加清晰和简洁,从配置界面上来看VIVAOD中ILA的配置也更为灵活,更便于用户使用,而ISE中需要用户加入较多的控制。下图是两者VIO调试IP核的对比,可以发现VIVADO下的使用更为方便和灵活。VIO具有虚拟输入输出的功能,不仅能够捕捉片上信号,而且也可以往片上输入信号。

二、 使用方法

我们需要在工程文件中加入调试IP核,同Chipscope类似,Hardware Manager可以通过HDL的方法来加入调试IP核,也可以通过网表的方法来插入调试IP核。我个人更倾向于前者HDL加入的方法,因为这样像使用普通IP核一样方便,省去在网表文件中苦苦寻找网线和寄存器的工作。

这里以HDL加入调试IP的方法为例来简要介绍,首先是根据需要配置好相应的调试IP核,如捕捉信号的数量及宽度、是否需要触发条件等等。然后,在代码中的相应位置进行实例化,连接需要捕获的信号或者输入的信号,如下图所示。最后,重新对该工程进行综合实现。

在工程中可以加入多个不同的调试IP核,以我个人的经验来看,只要加入调试IP捕捉的信号不是太多,整个工程的时序问题不会受到影响。当然,这也要看当前工程的时序情况以及资源利用情况。

三、 片上调试

综合实现完成之后,在工程的文件目录下会有xx.hw的文件夹,如上图所示,该文件夹中有捕捉信号的配置文件,能够将捕捉的信号自动对应到HDL代码中的信号变量名,这样省去了在使用Chipscope时的一些手动配置过程,给用户的使用带来了方便。

如下图,打开Hardware Manager,新建一个新的目标设备,此时会有一个选择目标设备位置的窗口,需要输入主机IP和端口号,所以,我们可以发现Hardware Manager不仅可以管理本机所连接的FPGA设备,也可以管理网络中其他主机所连接的FPGA设备。

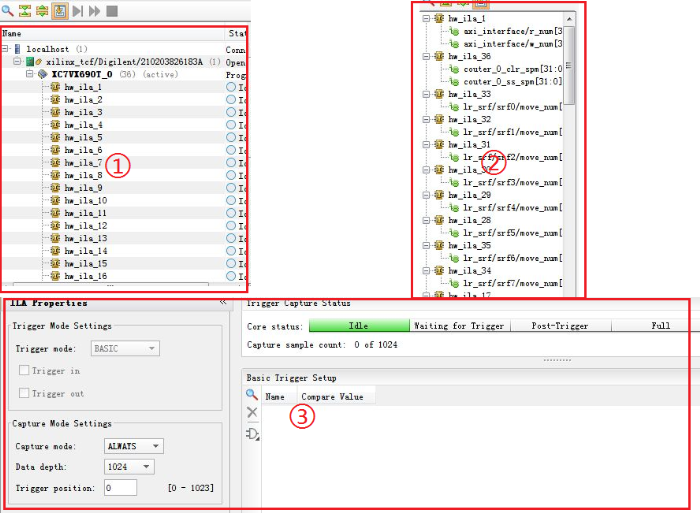

接下来是确认目标设备和配置传输波特率的两个窗口,在配置完成之后,就会弹出下图所示的调试窗口。其中,①是设备及调试逻辑的总的视图,②是所有调试IP的信息,③是每个调试IP核的状态极其配置的窗口。

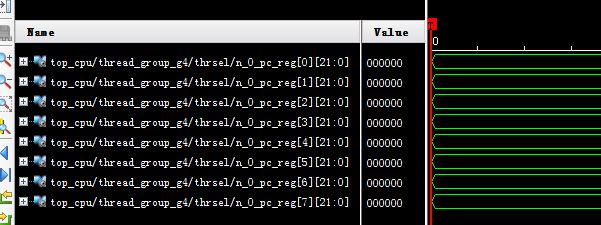

虽然在上图②中调试IP核的名字与代码中的有所不同,但是IP核捕获的信号名是没有变的,如下图所示。我们发现该调试窗口界面同行为级仿真的界面是完全相同的,且捕获的信号也方便用户分析,给用户的调试带来极大的便利。

由于笔者的开发经验不足,博文中可能存在一些认识上的错误,希望大家多多指正![]() 同时,也希望大家多多支持,你们的肯定是我努力的动力

同时,也希望大家多多支持,你们的肯定是我努力的动力![]()