基于FPGA的电压幅度测量(AD7476A)

0赞基于FPGA的电压幅度测量(AD7476A)

——两忘而化其道(fei199311)

〇、开篇前言

这次参加学校的校内电子设计比赛,负责电路测量模块的设计。本次设计初期,原想不会有太多问题,不过在设计过程中,发现了不少问题,主要是自己的问题-_-|||。

一、名词解释

AD转换:AD转换就是模数转换,也可以是整流。顾名思义,就是把模拟信号转换成数字信号。

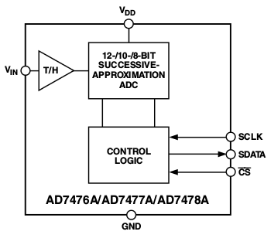

AD7476A:12位低功耗逐次逼近型ADC,采用单电源工作,电源电压为2.35V~5.25V,最高呑吐量可达1MSPS。模拟输入范围为0至VDD。转换速率取决于SCLK。

MSPS:Million Samples per Second。

转换速率(Conversion Rate):转换速率是指完成一次从模拟转换到数字的AD转换所需的时间的倒数。积分型AD的转换时间是毫秒级属低速AD,逐次比较型AD是微秒级属中速AD,全并行/串并行型AD可达到纳秒级。采样时间则是另外一个概念,是指两次转换的间隔。为了保证转换的正确完成,采样速率(Sample Rate)必须小于或等于转换速率。因此有人习惯上将转换速率在数值上等同于采样速率也是可以接受的。常用单位是ksps和Msps,表示每秒采样千/百万次(kilo / Million Samples per Second)。(1msps=1000 ksps)

二、设计需求

本次设计中,所需的测量的信号频率较低,所以用不到最高吞吐量,只需要完成SPI协议进行单向通信(从从机AD7476A到主机FPGA发生数据)。

三、设计思想

本设计分为三个主要的部分:数据获取、数据处理和数据显示模块。

数据获取模块,主要是从AD7476A得到数据。如图1中,除了电压和地,主机FPGA需要向从机AD7476A提供时钟SCLK,这个时钟根据设计需求定义;还有一个需要主机向从机发送的信号CS,需要注意的是这个信号是低电平有效的,详细设计需要参照Datasheet的时序图部分。

图1. AD7476A引脚定义

如下图2所示,图中所示的就是通信时序图。在设计电路时,需要严格按照时序图进行设计。更加详细的设计规则,需要参考Datasheet,这里就不赘述了。

图2. AD7476A通信时序图

数据处理模块原本想来是最简单的部分,不想在这里遇到了一些意想不到的问题,在设计方案中有这部分的详述。这个模块需要将数据采集部分的12bit数据除以4096,再乘以3.3V(Vdd)算出最终的电压值。

数据显示模块详见《FPGA_LCD1602_verilog》,http://blog.chinaaet.com/detail/37568。

四、设计方案

关于SPI协议的设计,有太多好的资料的,多去网上看看就好,这里写一些本次设计中SPI协议的注意点。首先本次设计是单向数据传输,所以只需要三根线;其次,时钟SCLK由主机控制,所以根据设计需求就可以调整SCLK,主机通过控制SCLK就可以完成对通信的控制;最后,数据是高位在前,低位在后。

在数据处理模块,需要实现除法,还要乘一个带小数点的数,这部分实现起来比较困难。

首先考虑除法,因为除法的除数是4096(=2^12)所以可以通过移位来实现,但是因为除出来的结果是小于1的数,所以这里考虑用定点数表示,由于整数部分最大值是3(需要两位二进制数),为了不损失精度,所以小数点之后需要12bit,共计14位。

其次考虑乘法的整数部分,3 = 2 + 1,这个简单的道理大家都懂,所以就简单了,把得到的12bit数据左移1位,再与原数相加,即可实现乘3操作。

最后考虑乘法的小数部分,还有一个公式就不是那么一眼就可以看出来了:3 ≈ 1/2^2 + 1/2^5 + 1/2^6 + 1/2^8,如此,将12bit原数据经过相应的右移,即可实现乘以0.3的操作。

这种逐次逼近的想法,应该说是非常重要的思想。

五、总结分析

本次设计的AD设计部分,基本是在零基础的情况下完成的,SPI协议以前也是没有深入了解过。AD模块用的是Digilent公司的Pmod AD1模块。AD模块的内容还是由很多的,由于这次实现为主,所以对原理和细节就没有那么注意了。

六、参考资料

[1] Analog Devices. AD7476A_DataSheet.pdf. 2004.