【原创】飞思卡尔MC9RS08KA2处理器管脚功能介绍

0赞最近稍微关注了一下飞思卡尔的八位低成本mcu MC9RS08KA2处理器,感觉不错,分享一下。首先要说一下这个低成本。这仅仅是对飞思卡尔来说的,飞思卡尔的处理器价格偏高,而且不好买,这是许多中小用户的共识。这里说的低成本指的是这款处理器在飞思卡尔所以处理器中价格相对偏低,应该是在两三块钱的样子,当然好的mcu的厂商把单片mcu的价格做到了10美分以下,所以飞思卡尔的这个芯片但就比价格是没有什么优势的。

好了,闲话少叙,转入正题

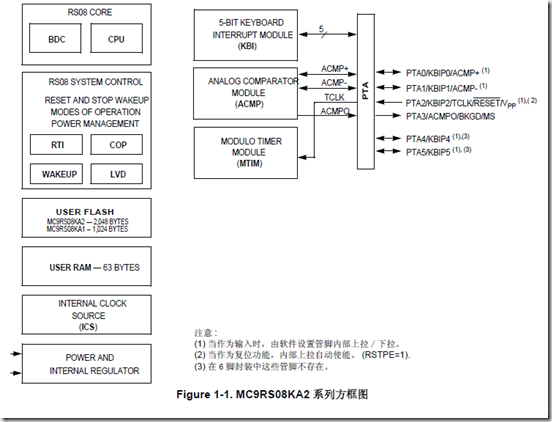

MC9RS08KA2 系列微控制器(MCU) 是一款极低成本、低管脚数的芯片,可用在家电、玩具和小设备等。这款芯片是由标准的片内模块构成,包括一个非常小的、高效的RS08 CPU 内核,63 字节大小的RAM,2K 字节大小的FLASH,一个8 位模定时器,键盘中断和模拟比较器。这款芯片有6 管脚和8 管脚两种封装。

处理器内部结构方框图:

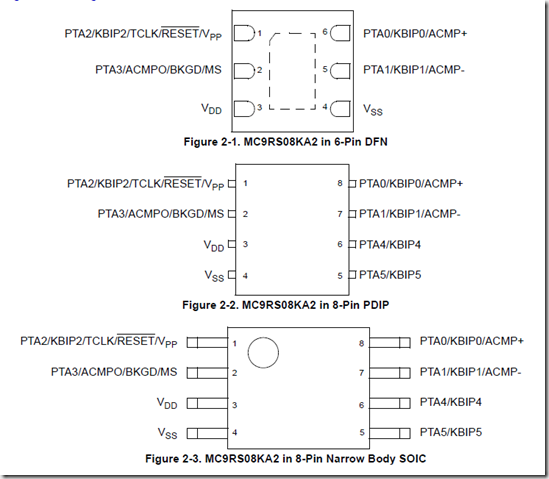

先来看看他的封装以及各管脚分布,这个芯片共有三种封装形式,分别是六脚QFN封装,八脚PDIP封装和八脚窄体SOIC封装。

关于这个芯片飞思卡尔给出了一个推荐的最小系统连接,想自己做板子或者用它开发产品的朋友不妨借鉴一下,这个连接图很简单,电源地之间加稳压电容和去耦电容 ,再加上一个bdm接口电路就可以了:

管脚详述:

1.电源

VDD 和 VSS 是 MCU 基本的电源管脚。这个电压源给所有的I/O 电路和内部参考电压调节器提供电源。内部电压调节器提供一个可调的更低电压源给CPU 和MCU 的其它内部电路。典型地,应用系统有两个独立的电容连接在电源管脚:一个大的电解电容,如一个10uF 胆电容,给整个系统提供大充电电荷;以及一个旁路电容,如一个0.1μF 陶瓷电容,放在离MCU 电源管脚最近的地方,用于抑止高频噪音。

2.PTA2/KBIP2/TCLK/RESET/Vpp

上电复位(POR) 进入用户模式后, PTA2/KBIP2/TCLK/RESET/VPP 管脚默认为输入管脚, PTA2。将SOPT 寄存器的RSTPE 置位,此管脚作为复位输入脚。配置为复位脚后,此管脚一直为复位脚,直到下次上电复位。当此管脚被拉低,复位脚以一个外部复位源复位 MCU。当被设置为复位脚(RSTPE = 1),内部上拉功能自动使能。

当执行FLASH 编程或擦除时,此管脚需要一个外部VPP 电压 ( 典型值 12 V) 。不管此管脚为何功能, VPP 接线总是连接到内部 FLASH 模块。当没有作为FLASH编程或擦除时,为了避免FLASH 过重负荷,外部VPP 电压必须被切断,并且高于 VDD 的电压必须避免。

注意

此管脚没有包含一个钳压二极管连接到VDD ,当没有执行 FLASH 编程或擦除时这个管脚的电压不能高于VDD 。

3. PTA3/ACMPO/BKGD/MS

作为只输出的PTA3 管脚的功能可以设置为背景调试或模拟比较输出。在复位期间,这个管脚功能模式可选择。复位后,这个管脚功能立即作为背景调试模式并且被用于背景调试通讯。在背景调试功能期间,这管脚有一个内部上拉使能。作为一个只输出端口,SOPT 寄存器中的BKGDPE 位必须被清零。

假如没有任何东西连接到这个管脚,MCU 在复位的上升沿期间进入到正常工作模式。假如有一个调试系统连接到6 管脚的标准背景调试头,在上电复位期间将BKGD/MS 一直拉低,强迫MCU 进入背景调试模式。

BKGD 管脚主要用于背景调试控制器(BDC)通讯,此通讯使用目标MCU 的BDC 时钟的16 个时钟周期的通讯协议。目标MCU 的BDC 时钟等于总线时钟。因此,大电容连接到BKGD/MS 管脚将会干扰背景串行通讯。

尽管BKGD 管脚是个假的开漏极管脚,背景调试通讯协议提供了暂时的、积极驱动的高速脉冲确保快速上升时间。来自电线的小电容和内部上拉设备在BKGD 管脚的上升和下降沿几乎不起作用。

4. 通用I/O 和外围端口

剩下的管脚都具有通用I/O 和芯片外设功能,如定时器和模拟比较器。上电复位后,所有这些管脚立即被设置为高阻态通用输入且内部上拉/ 下拉禁止。见下表