【原创】Freescale coldfire v1 单片机中断

0赞本篇博文将介绍飞思卡尔coldfire v1内核单片机的中断,并重点介绍外部引脚中断和实时中断,好戏开场了!

所谓的中断,就是当 CPU 正在处理某项任务的时候,在外界或内部发生了紧急事件,要求 CPU 停止正在处理的工作而去处理这个紧急事件,待处理完后,再回到原来中断的地方,继续执行原来被中断的程序,这个过程称作中断。

正常情况下,coldfire v1 MCU 按照用户程序指定的顺序有条不紊地执行代码。当有复位、定时器溢出等中断事件发生时,程序的运行次序会打破当前的程序流程,跳转到中断服务程序,直至中断处理完成后再转回被打断的程序处继续执行。

中断系统一般具有下面的操作:

1.能实现中断响应、中断服务和中断返回.当某一中断源发出请求时,MCU 将判断是否响应这一请求。如果允许响应这个中断请求,MCU 将通过硬件自动保护断点,转而执行相应的中断服务程序。中断处理完成后通过指令自动恢复断点,返回原中断处继续执行被中止的程序。

2.能实现中断优先级配置。当两个或更多个中断源同时发出中断请求时,优先级较高的中断请求首先得到处理。某些 MCU,如飞思卡尔的 S08 MCU 的中断优先级是固定的;而 coldfire v1 系列则提供有限的优先级调整办法,详细情况请参考“中断控制器教程”。在实际的微控制器应用系统中,外部端口的某些变化会比其他异常重要的多,比如复位信号、外部中断信号等。

3.能够实现中断嵌套。中断处理过程中,有优先级较高的中断请求时,MCU 能暂停正在执行的中断处理程序,转去响应和处理优先级较高的中断请求,结束后再返回原先优先级较低的中断处理过程。

4.能通过软件实现模拟中断的功能。该功能便于中断的调试。比如 S08 微控制器具有软件调试中断指令 SWI,可用于 MCU的调试开发。

具体关于 coldfire v1 系列的 MCU 中断这块的详情,在专门的教程“中断控制器教程”中描述,这里大家只需要理解中断的一般原理即可。下面重点说明 IRQ 引脚中断。

1.外部中断引脚 IRQ

外部中断引脚 IRQ 是coldfire v1 MCU 唯一仅作中断使用的外部引脚(KBI输入也可以当作是外部中断引脚,但还是有点不一样)。当 IRQ 中断使能后,IRQ可以用于唤醒 STOP 模式下的MCU。

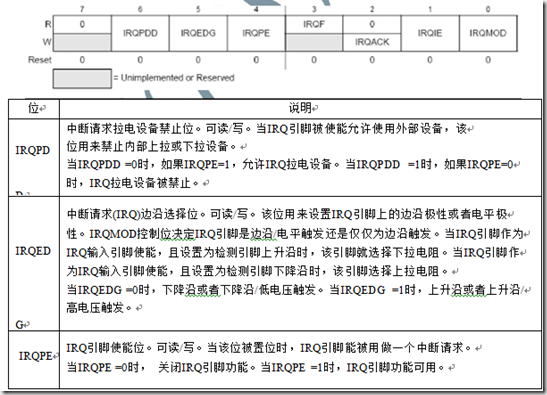

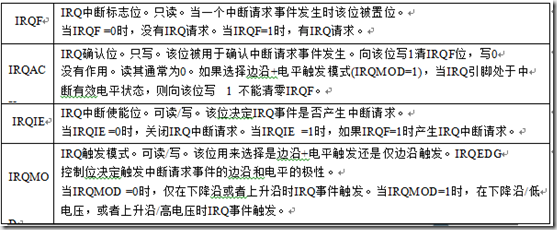

在MCU内部,外部中断引脚 IRQ 具有上拉电阻,当 IRQ 引脚使能时默认使用内部的拉电设备(IRQPDD=0),是上拉还是下拉由选择的极性决定。该引脚具有仅边沿触发模式和边沿+电平触发模式两种。由 IRQ 引脚的状态和控制寄存器IRQSC(Interrupt Pin Request

Status and Control Register)的IRQMOD控制位负责设置外部中断输入信号是边沿有效还是电平有效。参见表3。

在边沿+电平触发模式下,当检测到有效的边沿信号时,IRQF 状态标志位就会被置位,但只要 IRQ 引脚上的电平一直处于有效的触发电平状态,这个标志位就会持续被置位。

当把IRQ引脚配置为IRQ 输入时,BIH 和 BIL 指令可用于检测 IRQ 引脚的电平。

表3:外部中断引脚状态和控制寄存器(IRQSC)

2. 实时中断RTI

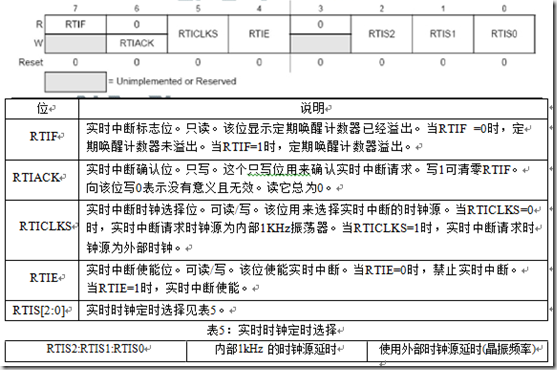

实时中断功能经常用来产生定期中断事件,由系统实时时钟状态和控制寄存器SRTISC(System Real-Time Interrupt Status and Control Register)进行管理。

该实时中断的时钟源可选择 1 kHz 内部时钟源或外部时钟。1 kHz 内部时钟源是一个独立的时钟源,在MCF51AC128单片机中可用于RTI模块和COP模块。如果使用外部时钟源,则必须对相关控制位进行设置。SRTISC 的 RTICLKS 位是用来选择 RTI 时钟源。

实时中断在正常模式、等待模式或STOP3模式下可以使用内部时钟源或外部时钟源。如果在STOP3模式中使用外部晶振,必须设置OSCSTEN=1,RANGE=0。只有选择内部时钟源,才能唤醒处于STOP2模式下的MCU。

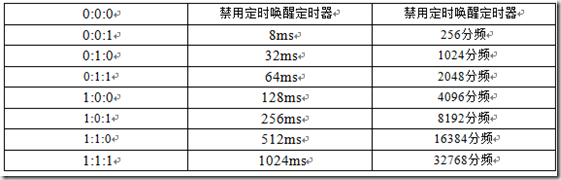

寄存器 SRTISC 包括一个只读状态标志位,一个只写确认位,和一个 3位的控制值(RTIS2: RTIS1:RTIS0),用于选择 7 个种唤醒间隔之一。同时这3个控制位也用于关闭实时时钟的时钟源。RTI的本地中断使能 RTIE 可用于屏蔽实时中断。表4给出了系统实时中断状态和控制寄存器(SRTISC)的细节信息。

表4:系统实时中断状态和控制寄存器(SRTISC)

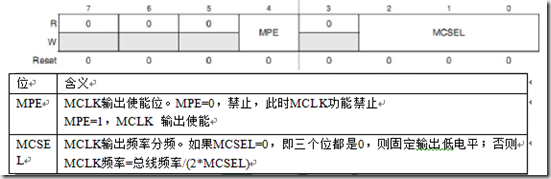

3. MCLK输出

MCLK输出是与PTC2复用引脚的。正常情况下,如果MCLK输出被禁止,该引脚由PTC对应的GPIO寄存器控制,但一旦使能MCLK,则无论GPIO寄存器怎么设置,这个引脚都会被配置为输出模式,其输出为MCLK时钟信号。MCLK时钟信号(即一定频率的方波)的频率与bus clk有关,具体说是BUS CLK频率的分频。所有这些都是由下面这个SMCLK寄存器控制的。