【原创】kinetis系统时钟-finial-实例解析

0赞之前的几篇博文里面详细而系统的介绍了kinetis处理器所用的时钟系统及其工作模式,这篇博文作为这个系列的总结,将介绍几个kinetis常用的时钟配置实例。

在这里我们将着重介绍两个实例,配置完成后设置 通过Flex总线将时钟输出,然后通过示波器来测量这个时钟的周期。

1.pee实例

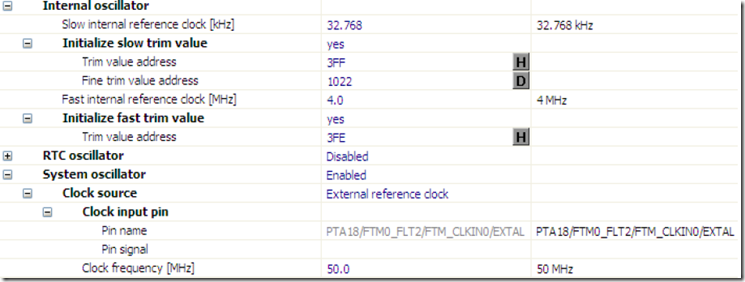

步骤一: 配置时钟,如图所示

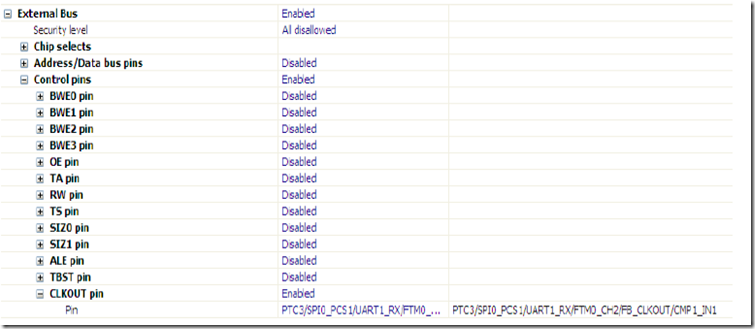

步骤二: 配置Flex总线上的时钟输出引脚,如图所示

配置完成后就可以自动生成相应代码,如下图所示:

/* 系统时钟初始化 */

/* SIM_SCGC5: PORTC=1,PORTA=1 */

SIM_SCGC5 |= (uint32_t)0x0A00UL; /* 使能引脚的时钟 */

/* 内部时钟校准 */

if ( *((uint8_t*) 0x03FFU) != 0xFFU) {

MCG_C3 = *((uint8_t*) 0x03FFU);

MCG_C4 = (MCG_C4 & 0xE0U) | ((*((uint8_t*) 0x03FEU)) & 0x1FU);

}

SIM_CLKDIV1 = (uint32_t)0x01130000UL;

SIM_CLKDIV2 &= (uint32_t)~0x0FUL;

SIM_SOPT2 &= (uint32_t)~0x00010000UL;

SIM_SOPT1 &= (uint32_t)~0x00080000UL;

PORTA_PCR18 &= (uint32_t)~0x01000700UL;

/* 切换到PBE模式 */

OSC_CR = (uint8_t)0x80U;

SIM_SOPT2 &= (uint32_t)~0x01UL;

MCG_C2 = (uint8_t)0x20U;

MCG_C1 = (uint8_t)0xAAU;

MCG_C4 &= (uint8_t)~(uint8_t)0xE0U;

while((MCG_S & MCG_S_IREFST_MASK) != 0x00U) {

}

/* 等待外部参考时钟选为MCG输出*/

while((MCG_S & 0x0CU) != 0x08U) { }

/* 切换到PBE模式 */

OSC_CR = (uint8_t)0x80U;

SIM_SOPT2 &= (uint32_t)~0x01UL;

MCG_C1 = (uint8_t)0xAAU;

MCG_C2 = (uint8_t)0x20U;

MCG_C5 = (uint8_t)0x18U;

MCG_C6 = (uint8_t)0x58U;

/* 等待外部参考时钟选为MCG输出*/

while((MCG_S & 0x0CU) != 0x08U) { }

/* 等待锁住 */

while((MCG_S &MCG_S_LOCK_MASK)==0x00U)

{ }

/* 切换到PEE模式 */

OSC_CR = (uint8_t)0x80U;

SIM_SOPT2 &= (uint32_t)~0x01UL;

MCG_C1 = (uint8_t)0x2AU;

MCG_C2 = (uint8_t)0x20U;

MCG_C5 = (uint8_t)0x18U;

MCG_C6 = (uint8_t)0x58U;

/* 等待直到PLL时钟输出选中 */

while((MCG_S & 0x0CU) != 0x0CU)

{ }

SIM_SCGC7 |= (uint32_t)0x01。

SIM_SOPT2 &= (uint32_t)~0x0300UL;

FB_CSMR0 &= (uint32_t)~0x01UL;

FB_CSMR1 &= (uint32_t)~0x01UL;

FB_CSMR2 &= (uint32_t)~0x01UL;

FB_CSMR3 &= (uint32_t)~0x01UL;

FB_CSMR4 &= (uint32_t)~0x01UL;

FB_CSMR5 &=(uint32_t)~0x01UL;

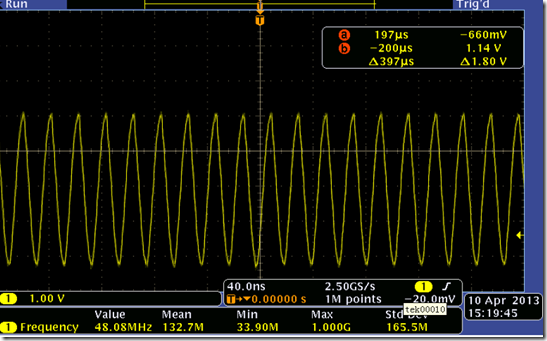

第四步,接下来使用示波器查看flex总线相应引脚上输出的时钟波形,如下图

2.FEI

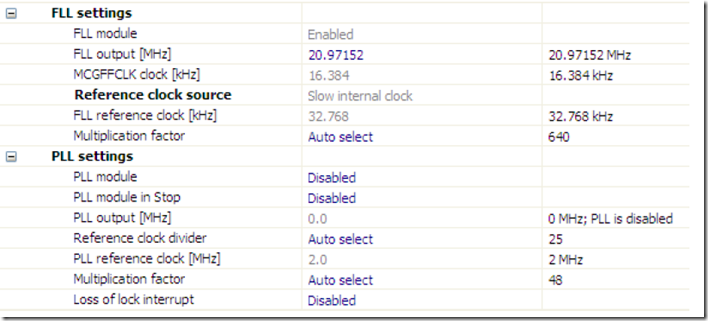

步骤一: 配置时钟,如下图

步骤二: 配置Flex总线上的是时钟输出引脚,配置同上

自动生成程序代码如下:

/* 系统时钟初始化 */

SIM_SCGC5 |= (uint32_t)0x0A00UL;

/* 内部时钟校准*/

if ( *((uint8_t*) 0x03FFU) != 0xFFU) {

MCG_C3 = *((uint8_t*) 0x03FFU);

MCG_C4 = (MCG_C4 & 0xE0U) | ((*((uint8_t*) 0x03FEU)) & 0x1FU);

}

SIM_CLKDIV1 = (uint32_t)0x00UL;

SIM_CLKDIV2 = (uint32_t)((SIM_CLKDIV2 & (uint32_t)~0x0EUL) | (uint32_t)0x01UL);

SIM_SOPT2 &= (uint32_t)~0x00010000UL;

SIM_SOPT1 &= (uint32_t)~0x00080000UL;

/* 切换到FEI模式*/

MCG_C1 = (uint8_t)0x06U;

MCG_C2 = (uint8_t)0x00U;

MCG_C4 &= (uint8_t)~(uint8_t)0xE0U;

OSC_CR = (uint8_t)0x80U;

SIM_SOPT2 &= (uint32_t)~0x01UL;

/* 检查FLL的参考时钟源是内部参考时钟*/

while((MCG_S & MCG_S_IREFST_MASK) == 0x00U) {

}

while((MCG_S & 0x0CU) != 0x00U) { /* Wait until output of the FLL is selected */

}

SIM_SCGC7 |= (uint32_t)0x01UL;

/*初始化外部总线模块*/

SIM_SOPT2 &= (uint32_t)~0x0300UL;

FB_CSMR0 &= (uint32_t)~0x01UL;

FB_CSMR1 &= (uint32_t)~0x01UL;

FB_CSMR2 &= (uint32_t)~0x01UL;

FB_CSMR3 &= (uint32_t)~0x01UL;

FB_CSMR4 &= (uint32_t)~0x01UL;

FB_CSMR5 &= (uint32_t)~0x01UL;

波形图如下:

好了,kinetis系统时钟就说这么多,如有疑问或问题可留言给我,也可访问飞思卡尔:

官方网站:www.freescale.com.cn

K60参考手册;

http://cache.freescale.com/files/32bit/doc/ref_manual/K60P100M100SF2V2RM.pdf?fpsp=1&WT_TYPE=Reference Manuals&WT_VENDOR=FREESCALE&WT_FILE_FORMAT=pdf&WT_ASSET=Documentation

TWR-K60N512开发板相关资料;

www.freescale.com/TWR-K60N512