电路时序问题

0赞我们常说“时序就是一切”。在复杂电路设计中,经常会有贯穿整个电路的总线信号。在某些情况下,要求这些信号必须完全一致。这些情况包括:

1. 视频图像的3色(红、绿、蓝)必须同时到达接收装置,否则视频图像将会变形。

2. 两路差分信号必须等长,并且这两个相反的信号必须同时到达接收端,否则会产生工模噪声。

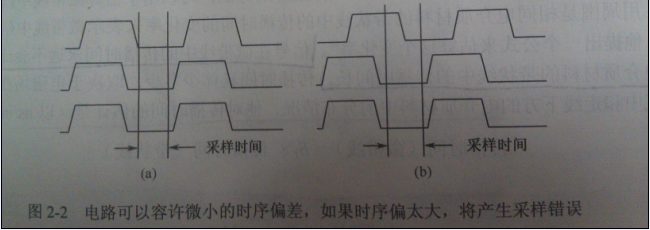

3. 当时钟脉冲信号触发时,数据信号必须稳定地出现在相应的端口,否则将出现数据错误。

图2-2(a)画出了在有时序错误时,可能发生的情况。图中画出了3个信号线,最上面的一个和其他两个稍有不一致。有一个时钟脉冲在对这几个数据进行采样。虽然数据信号并不是特别一致,不过时钟信号还是可以在它们都为低电平或者高电平时进行采样。在图2-2(b)中,最上面的信号和其他两个信号发生了严重的不一致,在时钟信号的采样周期中,它发生了电平跳变。所以在图2-2(b)中,将会发生数据逻辑错误。

多种原因都可以导致信号时序的不一致。器件本身就可以导致这一点。信号穿过某个器件时,有一个最快时间。每个器件的时间参数都不相同,而信号传播时要在电路上穿过多个器件。走线本身也会有传播延时。但是,在电路和系统中,对于某个特定的时间和位置,要求信号必须一致。电路设计工程师会对此提出要求,如何实现它就是电路板设计者的责任了。

电路板设计者通过走线的长度来控制信号的时序。通过增加走线的长度,可以增加走线的传播时间(以ns/in为单位)。如果我们需要某段走线有一个固定的延时,可以通过调整走线长度来实现。这个过程通常称为调节走线。

用这种方法调整时序有两个要求:a. 对信号在我们感兴趣的走线上的传播速度有精确地了解;b. 能够调整走线的长度。在前面的讨论中我们定义了传播速度,定义中涉及走线周围的材料的相对介电常数()。虽然我们不能让走线变得比两个端点间的距离还短,但是我们可以让它变得更长。调整走线长度的常用方法是用“蛇形”走线。

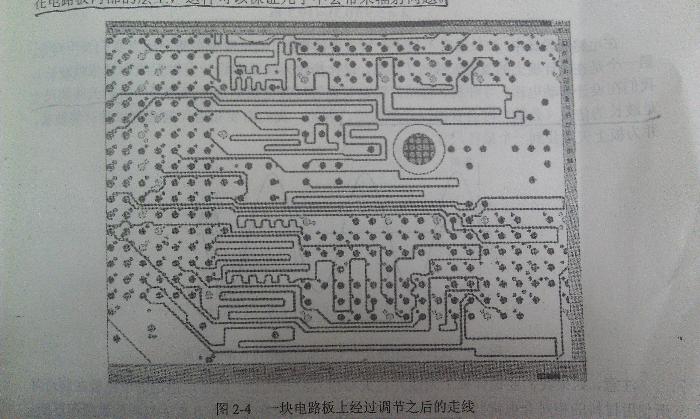

很多高端的PCB(印制电路板)涉及软件都会在用户给定合适的参数后自动调整走线的长度。图2-3给出了某个工具软件的调节编辑界面。可以看到允许设计者选择各种不同的模式。图2-4给出了ultracad design公司设计的电路板的一部分,在这个设计中很多地方都要求考虑调节走线。

一些工程师担心这些调节方法会引起EMI(电磁干扰)辐射。在实践中,只要注意以下几点,还没有发现过任何的EMI辐射问题。这些注意事项包括:a. 每条走线都有一个单独的参考层;b. 调节仅限于带状线信号层。不过在很多情况下,也会调节微带线层的走线(注意几乎所有计算机的主板)。但是如果确实担心调节引起EMI问题,那就把调节仅限制在电路板内部的层上,这样可以保证几乎不会带来辐射问题。

应该注意的是,有些文章指出调节回路之间的串扰会影响信号的传播速度,从而影响时序的计算。选中情况只可能在特别高频率的时钟信号下发生,这超出了本书的讨论范围。我们知道有很多人争论在计算传播时间时是否应该把过孔的长度也考虑进去。现在业内对此没有一个确定的结论。