Vivadoz中block memory Generator的使用方法

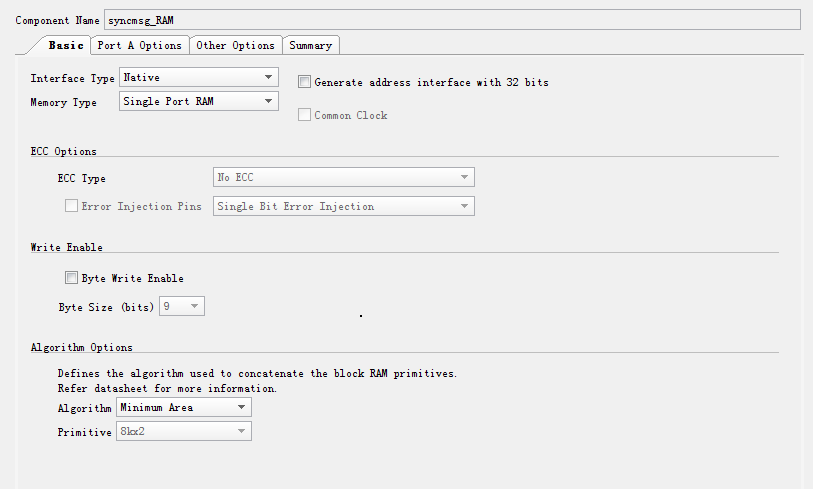

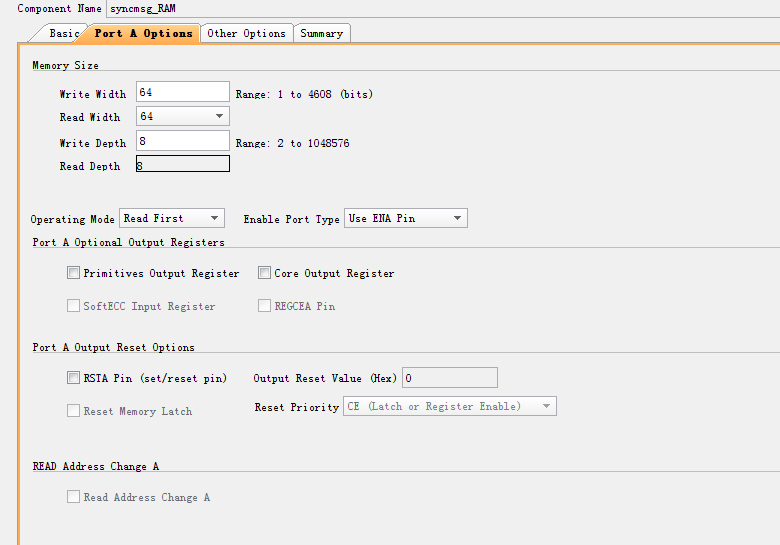

0赞在我们的项目中使用的是单端口RAM,读优先模式。其相关配置如下图所示。

我们采用OOC的方式对其综合。

查看官方文档,对操作模式的解释如下:

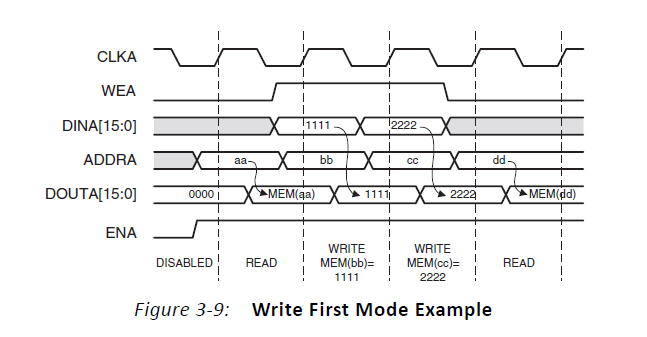

1、 写优先。

及在一个有效的clk上升沿到来时,先将DIN上的数据写入到ADDRA对应的地址中,然后再将ADDRA对应地址中的数据读出。其时序图入下所示。

可以看出,在写使能信号无效时读出的是ADDRA对应地址中原始的数据,在写使能信号有效后,读出的即为在该时钟写入的DIN 的新数据。

2、 读优先。

即在一个有效的clk上升沿到来时,先将ADDRA对应地址中的原始数据读出,然后再将DIN上的数据写入到ADDRA对应的地址中。其时序图入下所示。

从时序图中,我们可以看出,只要使能信号(ENA)有效,输出数据(DOUT)都是地址中的原始数据,先读出原始数据后,再将DIN中的数据写入到对应地址中。

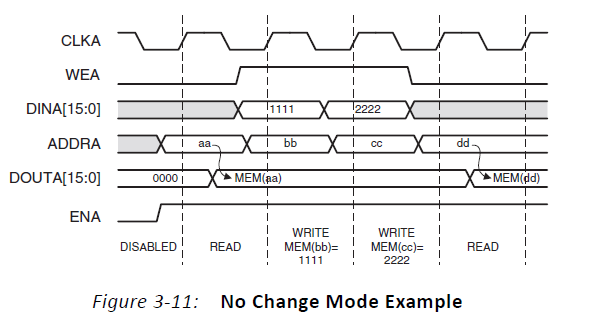

3、 不变模式(No Change Mode)

即在写使能信号有效时,也即在写入数据时,输出端口(DOUT)上的数据不会发生改变。其时序图如下所示。

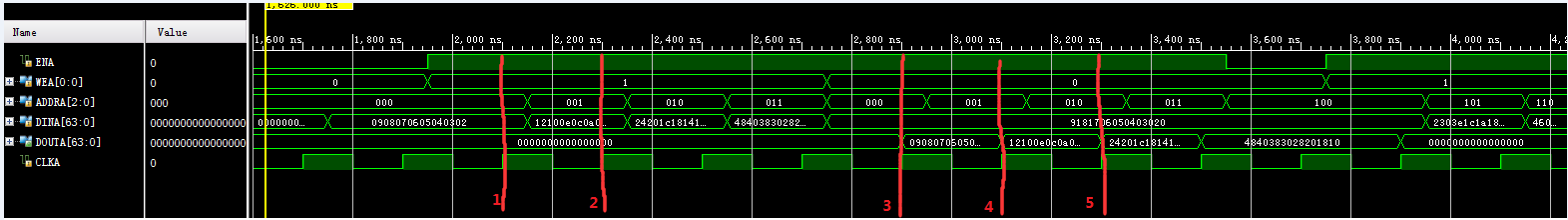

我们采用OOC的综合方式方式生成IP核,通过打开例子工程,可以对其单独进行仿真。先对该IP核单独仿真的时序图如下所示。

从图中可以看出,在第一条红色线标记的clka上升沿处,数据被写入到地址为000的内存中。在第一条红色线标记的clka上升沿处,数据被写入到地址为00的内存中。而由于采用读优先模式,在第一条红色线标记的clka上升沿处和在第而条红色线标记的clka上升沿处对应地址中还没有被写入数据,故dout端口数据为0.

在第三条红色线标记的clka上升沿处,地址为000的内存已经在第一条红色线标记处被写入数据,故此时dout端口上的数据为第一条红色线标记处写入到000地址的数据。