Vivado Implementation 1

0赞Vivado Implementation 1 : Implementation introduction

第一次发文,先自我介绍一下,我在某IC公司从事FPGA原型验证工作,使用的都是Virtex7 2000T型的FPGA,所以对Vivado有比较深入的接触。总体来讲,Vivado的功能比ISE要强大很多,但也确实有不少缺陷,而且也比较难上手。

我在Vivado的使用中,主要是用Vivado来实现Implemation,并不用它来synthesis,也不用它来simulation。synthesis tool我选用的是synplify,所以我的这些文章里都是以用synplify synthesis的netlist来run implementation flow的,Vivado版本为2014.4。

1.Create Project

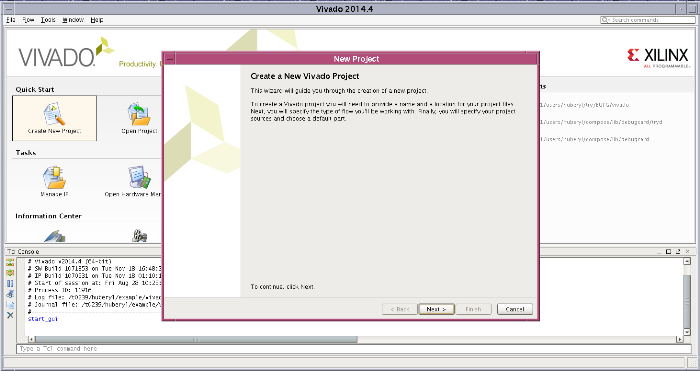

Create Project有GUI和tcl两种模式,我们先介绍GUI模式。对于新手推荐使用GUI,当比较熟悉的时候建议尝试tcl,会极大地提高工作效率。

Create New Project

如果勾选“Create project subdirectory”,则会以Project name为名字再创建一级子目录。

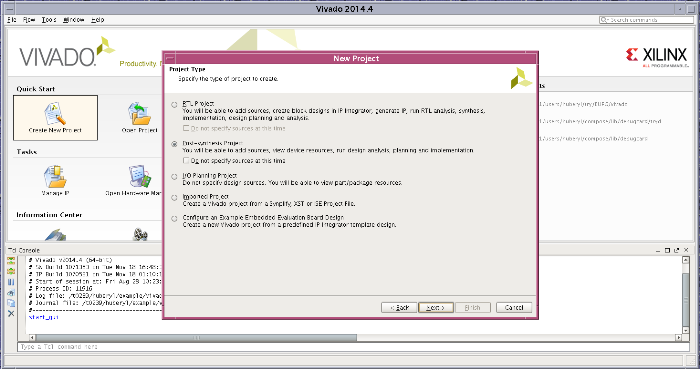

选择Post-synthesis Project。在这里顺便介绍一下其他几个选项,RTL Project就是以rtl为input,也就是说要使用Vivado来synthesis。I/O Planning Project比较特殊,无需rtl,在我看来主要是用于项目前期了解一下器件,以及try一下pin脚分布。

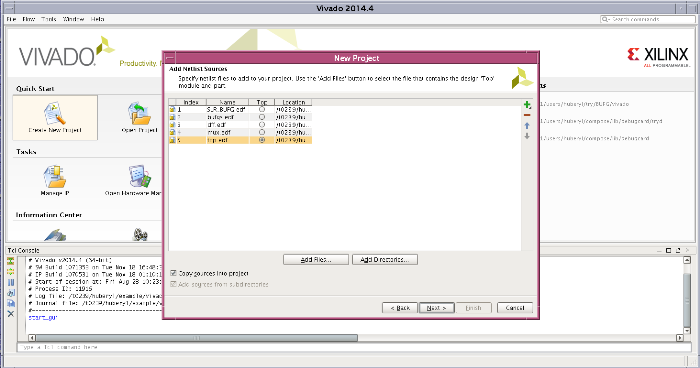

add netlist source。注意,一定要指定top netlist,在我这个例子里就叫top.edf。另外,”Copy sources into project”,是默认勾选的,建议将netlist copy到vivado目录下。

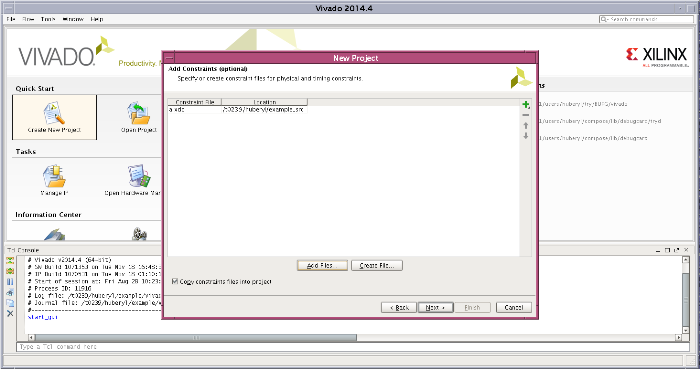

add constraints。如果有多个constraint,那么是按照顺序来执行的。另外,同样默认勾选了”Copy constraints files into project”。

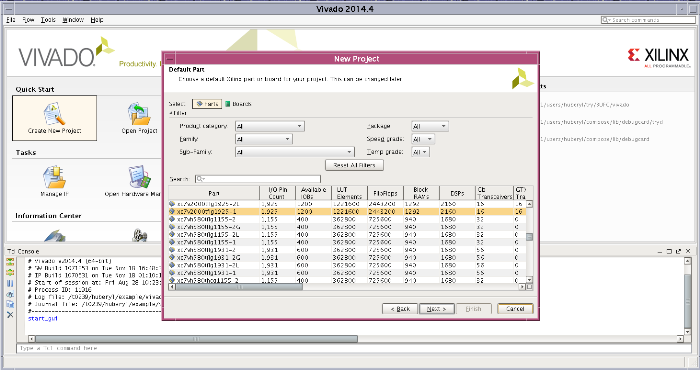

选择器件

2.Prepare Implementation

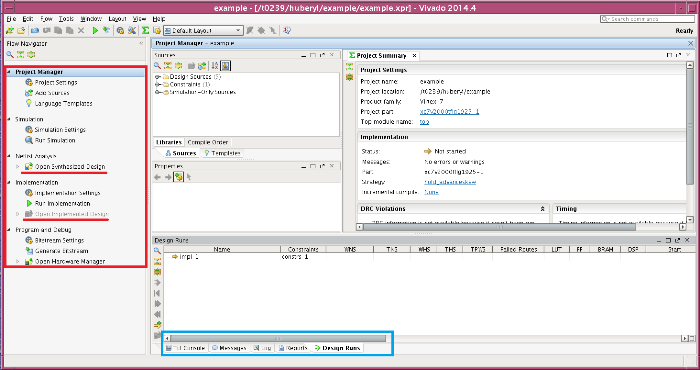

刚刚create project之后,如下图。下方的蓝框,显示不同的信息,比较重要的是Tcl Console,你所做的每一步,都在这个窗口将其对应的tcl显示出来,对于学习vivado tcl有很大帮助。

在这里我介绍两个极为重要的概念:Synthesized Design和Implementationed Design。

由于我的flow是使用已经综合好的netlist作为input,所以Synthesiszed Design就是input netlist。如果我们要加debug signal或是对netlist作出以下修改等等,就必须Open Synthesiszed Design,也就是红框内的那个按钮,将netlist load到memory中,才能对其进行操作,比如set up debug。

run完Implementation的netlist,成为Implementationed Design,基于这份netlist,就可以直接generate bitfile,也可以用它来进行一个ECO。

由于我们刚刚创建了project,没有run implementation,所以没有Implementationed Design。因为没有Open Synthesized Design,所以此时memory中没有任何netlist。

这个时候,在你的目录下,就会自动创建两个文件夹*.cache和*.srcs,其中*就是你的project name。netlist和constraint都存放在了srcs目录下,如果你在vivado中修改了netlist或constraint,都是对srcs下的进行修改。而如果你对源文件进行了修改,是不会自动load的,你需要手动reload一下。

3.Implementation Strategy

如果你的design很简单,那请跳过此节。

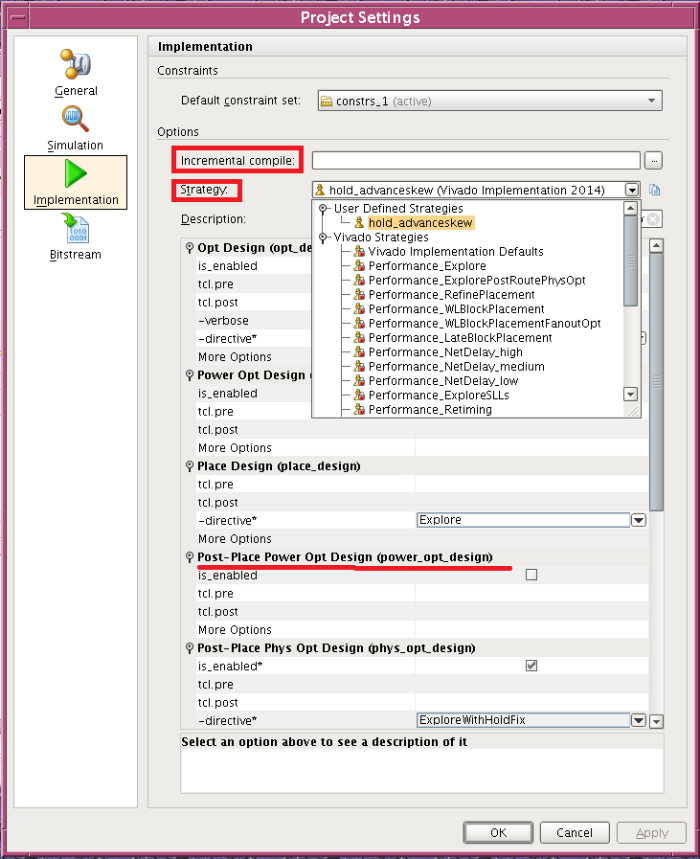

点击”Implementation Setting”,就会弹出如下界面。Implementation是一个比较复杂的过程,其中包括若干步骤,具体步骤的介绍我会单独写一篇博文来介绍(内容较多,比较复杂)。在这里我要简要介绍一些,有的步骤是必须的,而有的步骤是非必须的,比如图中的”Post-Place Power Opt Design(power_opt_design)”,如果没有勾选is_enable,那就不做这一步。而其中的”-directive”,则是由用户来指定不同的算法来实现。Vivado内部集成了很多Strategy,也就是图中的红框,用户可以自行选定,也可以自己定制最适用于自己的Strategy,比如我就定制了一个名为hold_advanceskew的Strategy。至于如何定制属于自己的专属Strategy,一方面要了解Vivado的各种Strategy,再有就是了解自己的design,多尝试集中Strategy,这样才能找到最适用于自己的Strategy。

另一个红框内的Incremental compile,是一个新功能。如果你的design只有很小的改动,那么以之前的checkpoint文件(.dcp)为指导,可以较快的完成Implementation。但我在实际使用中,发现局限较大。因为即使改动很小,一旦重新综合,很多net的名字都变了,这就造成实际的netlist改动并不小,所以并不会提升很多,甚至还会造成布线布不通的情况。不过,对于ECO,还是比较快的。

tcl.pre表示在这一步之前执行某一tcl,tcl.post表示在这一步之后执行某一tcl,这就给GUI模式下提供加载tcl提供了方便条件。在这里我介绍一个把ERROR降为Warning的tcl。在ISE中,不指定pin location是不会报ERROR的,而在Vivado中则不行,那么如果让Vivado对不指定pin location不报ERROR呢?在Bitstream的pre.tcl中,load一个tcl,命令如下:

set_property SEVERITY {Warning} [get_drc_check UCIO-1]

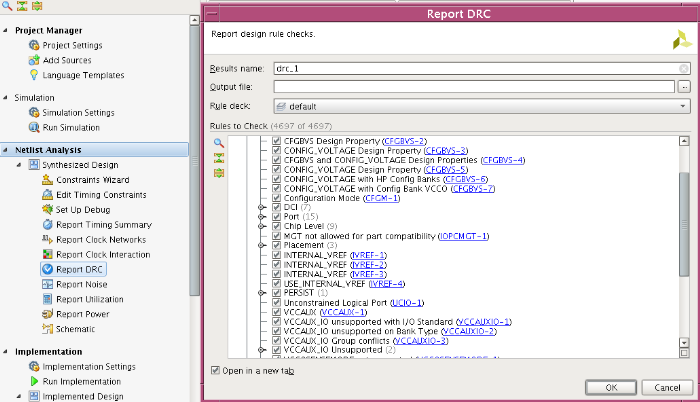

至于UCIO-1的含义,如下图。我们可以通过Report DRC来查看DRC的规则集。

4.Create multiple runs

上一节介绍了Implementation Strategy,如果我们需要对同一netlist同一constraint尝试不同strategy,或者是我们要尝试不同的constraint,是不是我们就要逐个手动run Implementation,记录结果,在进行比较呢?答案显然是否定的。

每次Create project之后,会自动Create一个runs,名字叫impl_1。我们要做的,就是Create多个runs。

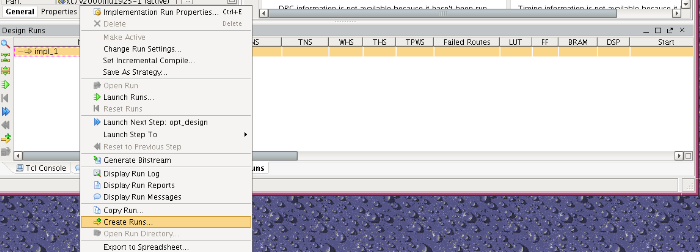

在Design runs窗口右键单击,弹出如下窗口,选择Create runs…。

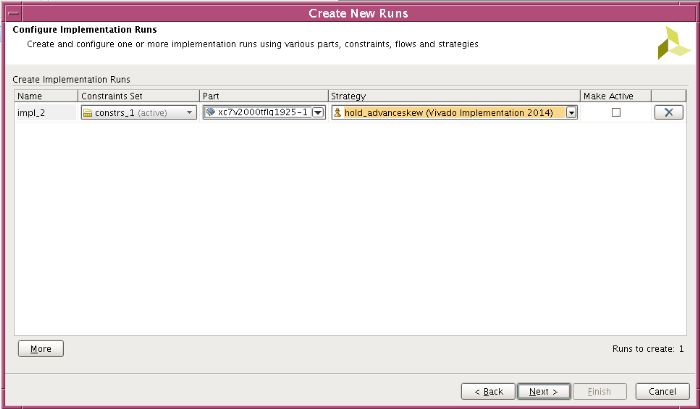

之后会弹出如下窗口,我们可以创建runs,并设置不同的constraint、Strategy。注意Make Active一项,一个project可以有多个runs,但是能有一个Make Active。导航栏的操作,都是对Make Active的runs进行的。

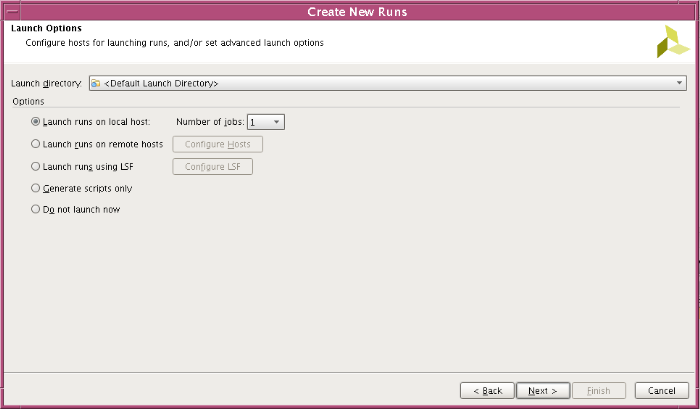

之后界面如下,Vivado可以在一台机器上并行run,也可以串行run,还可以登录远程服务器。点击Next,Create runs就完成了。

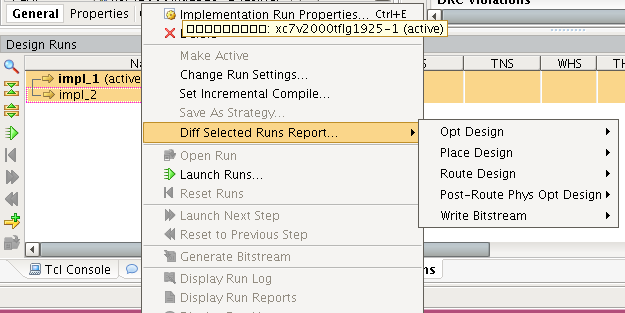

晚上的时间是极为充裕的,Create多个runs,下班前run上,第二天就都好了。不同的runs都存放在不同的目录,名字以runs的名字命名。我们还能勾选上多个runs,对比其结果有什么不同,如下图。

5.ECO

在FPGA中,有可能我们调试之后,发现只需要进行一处非常小的改动,比如对clock降频呀,把某一个逻辑取反呀等等。就需要修改RTL,重新synthesis、implementation、writebitstream。其实,Vivado的强大功能,使我们无需这么麻烦。

比如我们是用MMCM来产生clock,调试过后发现信号质量不好,想要尝试降频,我们所做的修改,实际上只是修改MMCM的一个参数,并不涉及修改连线。我们可以直接在已经生成bitfile的.dcp文件上,稍加修改即可。

刚开始使用Vivado时,我尝试过ECO。我的步骤是这样的,点击GUI中的Open Implementationed Design,然后修改相应的MMCM参数,最后点击GUI中的WriteBitstream按钮。可上板子上一测试,并没有降频。当时schedule比较紧,我就没有在做尝试,后来看了AllyZhou写的一篇Vivado ECO的文章,并阅读了大量的Xilinx User Guide,我才发现其中的问题。

首先,我先介绍一个.dcp文件。在Vivado中,记录数据的文件就是checkpoint,也就是.dcp文件。在Vivado Implementation的flow中,诸如Place、Route等等每一步都会生成一个.dcp文件。

其次,Vivado中,把Place、Route等都归入到Implementation中,所以实际上只有两大步:Implementation和WriteBitstream。当Implementation之后,如果我们点击GUI中的WriteBitstream按钮,注意,是点击按钮,这时候Vivado会load最后一个完成route的dcp文件。解释一下,首先,得是fully route的.dcp才能生成bitfile;其次route之后还有一个可选的步骤phys_opt_design,如果有run这一步,就会用这一步的.dcp,而不是route的。

所以,我之前ECO时,应该点击GUI中的WriteBitstream按钮来生成bitfile,而是应该使用tcl:write_bitstream a.bit。我没有试过修改Implementationed Design之后,保存一个.dcp文件,再点击GUI中的WriteBitstream按钮会怎样,因为我找到了更好的方法。

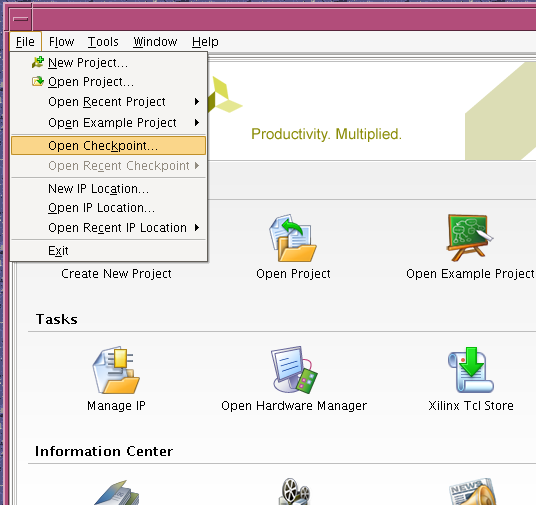

我们直接在原有的project中修改,database会比较混乱。所以,我将最后一个.dcp文件copy出来,新建一个目录,用Vivado直接打开这个.dcp文件,然后进行修改。在GUI中open checkpoint方法如下:

客观的说,Vivado在ECO方面,要比ISE时代的FPGA Editor要强大,但也确实不好入门。其实,这些方法都写在Xilinx那上千份User Guide中,但Xilinx并没有一个User Guide的目录。刚入门时,你可能都不知道如何检索出来,比较遗憾。