【嵌入式】VGA接口时序约束-中

0赞VGA接口时序约束-中

SF-VGA模块购买地址:http://myfpga.taobao.com/

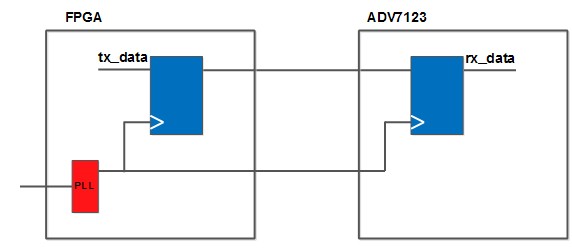

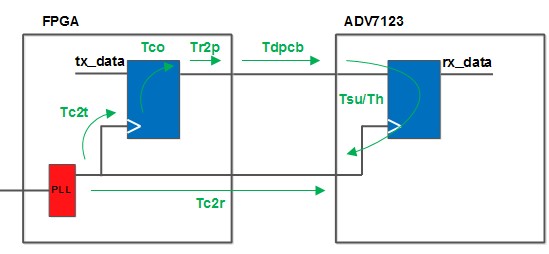

好,有了这些信息,我们可以分析一下这个接口的时序要求,然后对其进行约束。这个输出的信号,其实是很典型的源同步接口,它的时钟和数据都是由FPGA来驱动产生的。一般的源同步接口的寄存器模型如图所示。在我们的这个系统中,发送端是FPGA,而接收端是DA芯片ADV7123。如果传输的速率比较高,那么数据和时钟上升沿的严格对齐则要依靠PLL产生可调相位的时钟信号来保证。不过,我们这个25MHz或者50MHz的时钟通过较好的时序分析和约束后,则不必动用PLL。

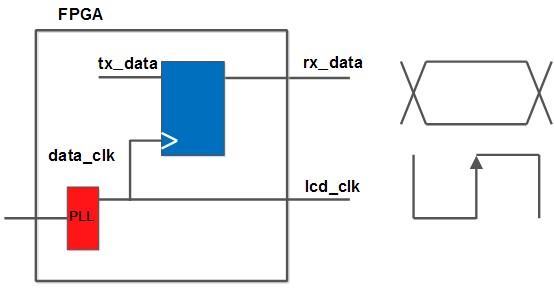

如图所示,FPGA产生的数据data_out和时钟clk_out的理想波形是时钟上升沿锁存到稳定可靠的数据。

下面我们来探讨如何对这个设计进行约束。首先,对系统的输入时钟、PLL产生的时钟进行约束。

create_clock -name {clk} -period 40.000 -waveform { 0.000 20.000 } [get_ports {clk}]

derive_pll_clocks –use_tan_name

以上的约束将会覆盖如下的时钟。

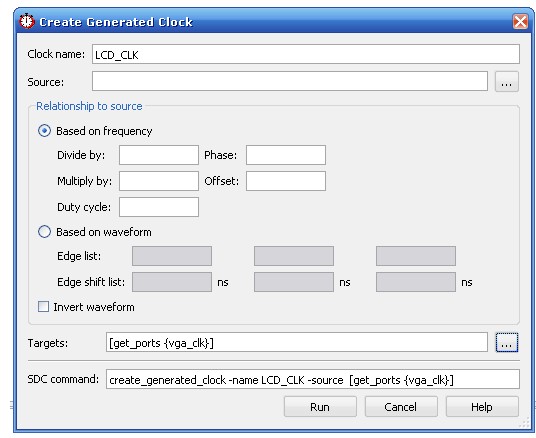

接着,对LCD_CLK这个时钟进行约束,它需要约束为虚拟(virtul)时钟,将会被用于output port上的数据锁存时钟。因为我们这个工程可能会用到25MHz的LCD_CLK,也会用到50MHz的LCD_CLK,因此我们以频率更高的50MHz为例进行说明。系统的50MHz是PLL的clk[1]输出的,因此我们约束这个虚拟时钟如下。

create_generated_clock -name LCD_CLK -source [get_ports {vga_clk}]

这个虚拟时钟将会在FPGA内部做tx_data的reg2pin时序分析时作为latch时钟。实际对于一般的reg2reg路径的分析,由于他们的launch和latch时钟都在FPGA内部,若像前面一样做过时钟的约束,那么FPGA对这些内部的时钟就已心知肚明,无需什么虚拟时钟。而对于pin2reg或reg2pin的路径分析,则一般都需要用户指定一个符合相关时钟要求的虚拟时钟。

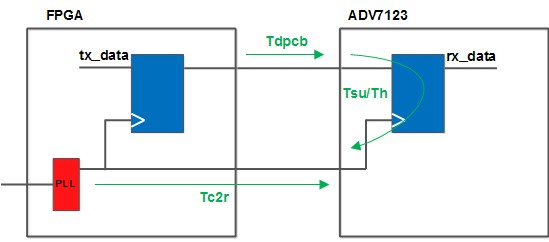

如图所示,有了时钟LCD_CLK,下面我们需要对数据总线进行约束,

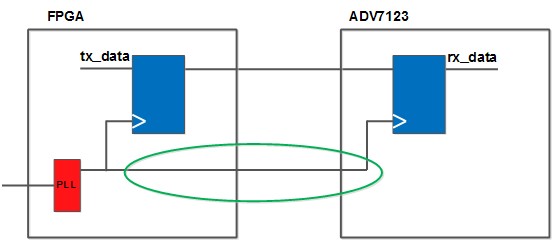

在这个图中,有两条关于时钟的路径延时,我们假设PLL输出的时钟是源和目的时钟的起点,以这个点为基准,时钟到达源寄存器,其路径延时为Tc2t;时钟达到ADV7123芯片的管脚,其路径延时为Tc2r,这个延时包括了时钟从PLL输出到FPGA管脚的延时以及时钟从FPGA的管脚到ADV7123的管脚的延时,后者的延时是PCB走线产生的延时。关于时钟的路径,首先是数据进入源寄存器的输入端口后,在源寄存器内部的一个延时Tco,接着是数据从源寄存器的输出端口到FPGA管脚上的延时,还有就是数据在PCB上的延时Tdpcb,最后在计算ADV7123的时序时,我们必须将数据的建立时间Tsu和保持时间Th考虑在内。

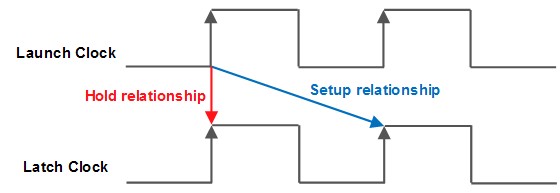

下面我们可以简单的来分析一下数据的建立时间和保持时间应该满足怎样的关系才能保证被LCD_CLK稳定的锁存到ADV7123内。首先,我们需要提一下时钟的launch edge和latch edge的概念。如图所示,对于一个源寄存器和目的寄存器传输时钟一致的理想路径,他们的launch edge和latch edge的示意如图。我们可以这么理解,对于setup时间,launch edge是latch edge的上一个时钟节拍,latch edge通常是要去采样launch edge已经采样过的数据。而对于hold时间,launch edge是latch edge通常是同一个时钟沿,latch edge的hold时间不被冒犯,也就意味着latch edge不采样它前一拍的数据。

对于建立时间,有:

Launch edge + Tc2t + Tco + Tr2p +Tdpcb < latch edge + Tc2r - Tsu

对于保持时间,有

Launch edge + Tc2t + Tco + Tr2p +Tdpcb > latch edge + Tc2r + Th

前面我们已经约束好了源时钟和目的时钟(虚拟时钟),因此,latch edge和launch edge是FPGA已经知道的参数。同样的,Tco和Tc2t、Tr2p、Tc2r的FPGA内部延时,也都是FPGA能够确定的,并且FPGA会通过设计者的约束,其控制这些内部的时序延时使得前面给出的两个基本公式得到满足。那么,就存在一个问题,FPGA并不知道这两个公式中FPGA外部的路径延时参数,我们下一步的数据路径约束要做的就是把这些参数告诉FPGA。Altera的TimeQuest中set output delay约束的功能就是要传递这个信息。我们下面来看看set output delay的值如何计算。

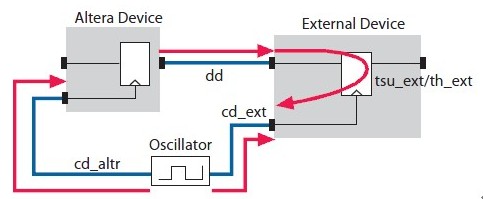

如图所示,这是Altera的Handbook给出了set output delay的max和min值计算方法。大家可要睁大眼睛瞧好了,下面我们就要变通一下,具体问题具体分析。

Output delay max = dd_max + tsu_ext + (cd_altr_min - cd_ext_max)

Output delay min = dd_min – th_ext + (cd_altr_max – cd_ext_min)

在我们的应用中,仿照官方的分析方法,我们也同样可以得到set output delay的计算公式。

Output delay max = Tdpcb_max + Tsu + (0 - Tc2r_max)

Output delay min = Tdpcb_min – Th + (0 - Tc2r_min)

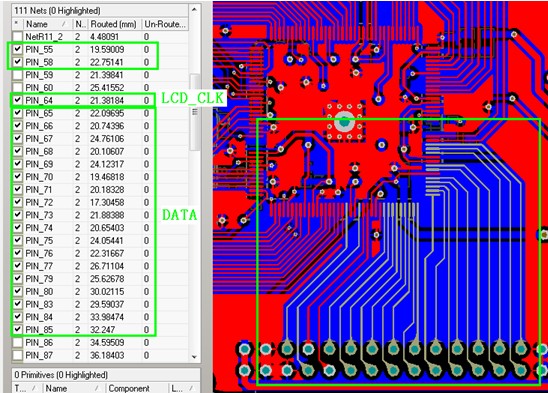

关于PCB的延时,我们可以看看SF-CY3核心板以及SF-VG子板上的这部分时钟和数据走线。如图,在SF-CY3核心板上,LCD_CLK的走线约为21.4mm,而其他数据总线的延时在17.3mm~34.0mm。

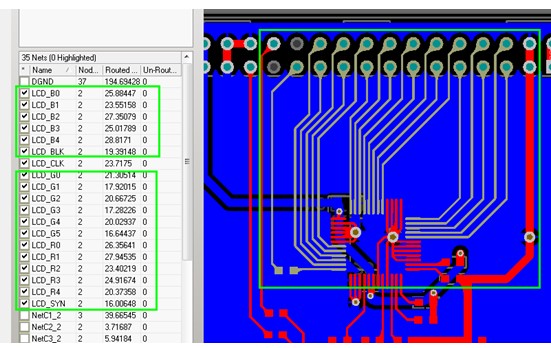

在SF-VGA子板上,我们看到LCD_CLK的走线约为23.7mm+5.0mm(匹配电阻的另一端,图中未显示数值)=28.7mm,而数据总线长度在16.0mm~28.9mm。

结合两个板子的走线延时,我们可以计算出LCD_CLK的走线总长约为50.3mm,数据总线的总长约为33.3mm~62.9mm。根据0.17ns/25.4mm的PCB走线延时进行换算可以得到,LCD_CLK的走线延时约为0.34ns,而数据总线延时约为0.22ns~0.42ns。

把我们的参数套进去,我们先不计算时钟偏斜(包括PCB的走线延时)那部分的参数,可以得到:

output max delay = 0.42ns + 0.2ns = 0.62ns

output min delay = 0.22ns – 1.5ns = - 1.28ns

接着,我们可以对VGA的信号做如下的约束。

set_output_delay -clock { LCD_CLK } -max 0.62 [get_ports {vga_b[0] vga_b[1] vga_b[2] vga_b[3] vga_b[4] vga_g[0] vga_g[1] vga_g[2] vga_g[3] vga_g[4] vga_g[5] vga_r[0] vga_r[1] vga_r[2] vga_r[3] vga_r[4] adv7123_blank_n}]

set_output_delay -clock { LCD_CLK } -min -1.28 [get_ports {vga_b[0] vga_b[1] vga_b[2] vga_b[3] vga_b[4] adv7123_blank_n vga_g[0] vga_g[1] vga_g[2] vga_g[3] vga_g[4] vga_g[5] vga_r[0] vga_r[1] vga_r[2] vga_r[3] vga_r[4]}]