FPGA-VIP视频工程开发连载2——NAND FLASH读写操作

0赞FPGA-VIP视频工程开发连载2——NAND FLASH读写操作

工程实例下载地址:http://pan.baidu.com/s/1hqJx3tM

功能简介

本实例在例程2的基础上,添加了一个自定义的NAND FLASH控制器组件,这个组件也是挂在Qsys系统的Avalon-MM总线上。NAND FLASH复杂的底层驱动时序都由这个控制器内部产生,无需NIOS II处理器直接参与。NIOS II处理器只需要通过Avalon-MM总线对相关寄存器进行读写就可以实现NAND FLASH的读写。

本实例和实例3一样,有3个大模块。

● Vip.v是顶层模块,其下例化了两个模块。

● Sys_ctrl.v模块中例化了PLL,并且对输入PLL的复位信号以及PLL锁定后的复位信号进行“异步复位,同步释放”的处理,确保系统的复位信号稳定可靠。

● Vip_qsys.v模块则是Qsys系统的例化。

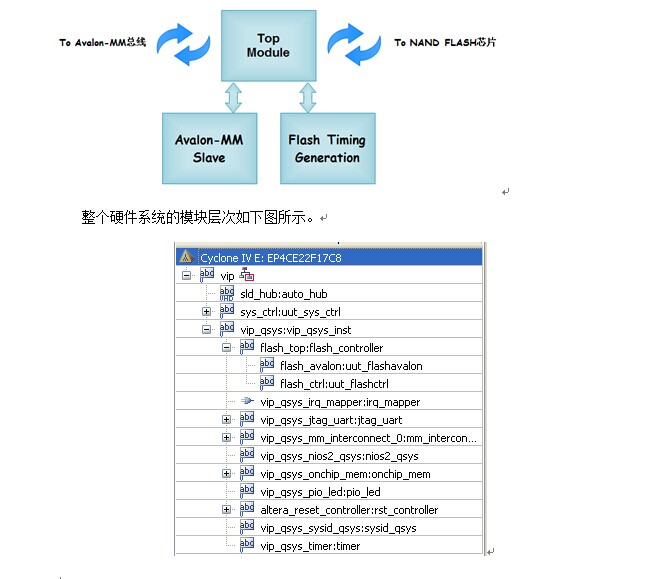

在Vip_qsys.v下面,挂着很多外设组件,也包括我们自己用逻辑搭建的NAND FLASH控制器组件。NAND FLASH控制器组件有3个模块,一个top模块,其下例化了两个子模块,分别作为Avalon-MM从机逻辑模块和Flash控制时序产生逻辑模块,如下图所示。

整个硬件系统的模块层次如下图所示。

实验说明

1. 打开光盘目录“…\prj\vip_ex4”下的工程。

2. 使用Programmer将“…\prj\vip_ex4\output_files”文件夹下的vip.sof文件下载到VIP板中,这是JTAG在线调试模式,此时VIP板上的指示灯D1一直处于熄灭状态。

3. 系统的程序菜单中找到“Nios II 13.1 Software Build Tools for Eclipse”(简称EDS)并打开。导入“…\prj\vip_ex4\software”文件夹下的软件工程(包括应用工程和BSP工程)。

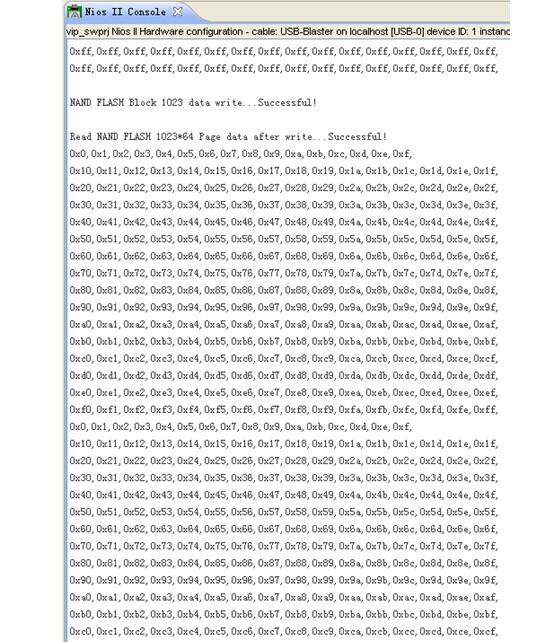

4. 运行应用软件,片刻后,可以看到Nios Console开始打印如下图所示的数据。完成打印后LED指示灯D1开始闪烁。在打印窗口中,我们可以看到本实例的软件执行了4个主要操作。

● 擦除NAND FLASH的第1023 Block的数据。

● 读出刚刚执行完擦除操作的NAND FLASH的第1023 Block的第1个Page数据。刚擦除完,都是0xff的数据。

● 产生一组0到255递增的数据写入到NAND FLASH的第1023 Block的第1个Page中。

● 写入完成后,读出这个Page的数据,以此确认写操作是否正确执行。

工程实例下载地址:http://pan.baidu.com/s/1hqJx3tM