FPGA实战演练逻辑篇11:时钟电路

0赞时钟电路

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

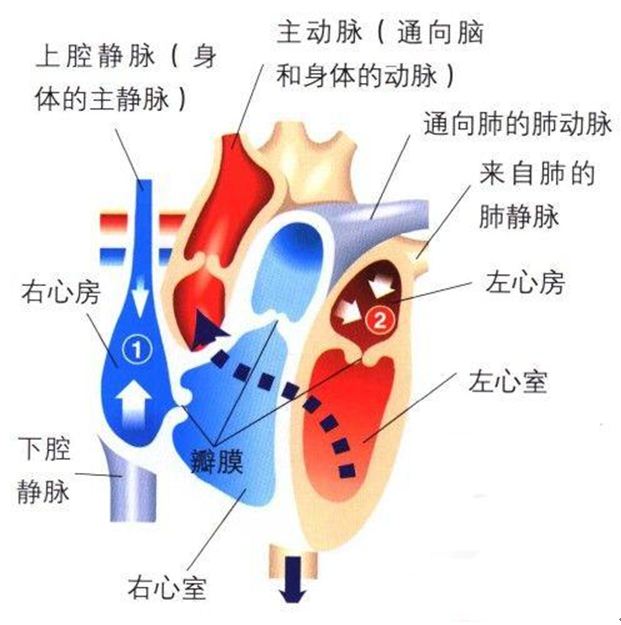

人体拥有非常奇妙的循环系统,而心脏是这个循环系统的发动机,它向全身各部位供应血液。如图3.5所示,心脏有四个空腔,上面两个叫心房(atrium),下面两个叫心室(ventric1e)。右心房收纳全身的静脉血,通过右心室从肺动脉泵出,此时肺动脉中流的是静脉血,通过肺中的气体交换,变成含氧丰富的动脉血,由肺静脉送至左心房,再通过左心室的主动脉泵向全身各个组织器官以满足其正常生理活动的需要。这便是人体无时不刻不在进行着的心跳过程。(特权同学,版权所有)

图3.5 心脏示意图

了解了心脏之于人体内部循环系统的作用,反观时钟信号之于FPGA器件,其实也有着异曲同工之妙。伴随着每一次的心跳过程,都有血液的运转和流动;同样的,伴随着每一个时钟脉冲的产生,也都有数字信号的输入和输出。对于在FPGA器件内实现的任何时序逻辑应用,失去了时钟信号便意味着信号的传输将处于停滞状态。时钟信号的重要性可见一斑。(特权同学,版权所有)

图3.6 理想时钟波形

FPGA器件的时钟信号源一般来自外部,我们通常使用晶体振荡器(简称晶振)产生时钟信号。当然了,一些规模较大的FPGA器件内部都会有可以对时钟信号进行倍频或分频的专用时钟管理模块,如PLL或DLL。由于FPGA器件内部使用的时钟信号往往不只是供给单个寄存器使用,因为在实际应用中,成百上千甚至更多的寄存器很可能共用一个时钟源,那么从时钟源到不同寄存器间的延时也可能存在较大偏差(我们通常称为时钟网络延时),而我们知道,这个时间差过大是很要命的。因此,FPGA器件内部设计了一些称之为“全局时钟网络”的走线池。通过这种专用时钟网络走线,同一时钟到达不同寄存器的时间差可以被控制到很小的范围内。而我们又如何能保证输入的时钟信号能够走“全局时钟网络”呢?有多种方式,对于外部输入的时钟信号,只要将晶振产生的时钟信号连接到“全局时钟专用引脚”上;而对于FPGA内部的高扇出控制信号,通常工具软件会自动识别此类信号,将其默认连接到“全局时钟网络”上,而设计者若是不放心,也可通过编译报告进行查看,甚至可以手动添加这类信号。关于时钟电路的设计和选型,有如下几个基本事项需要考虑:

● 系统运行的时钟频率是多少?(可能有多个时钟)

● 是否有内部的时钟管理单元可用(通常是有)?它的输入频率范围(需要查看器件手册进行确认)?

● 尽可能选择专用的时钟输入引脚。(特权同学,版权所有)

● 时钟走线尽可能短,有条件最好做包地处理,确保外部输入时钟信号干净、稳定。(特权同学,版权所有)