FPGA实战演练逻辑篇51:建立时间和保持时间

1赞建立时间和保持时间

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

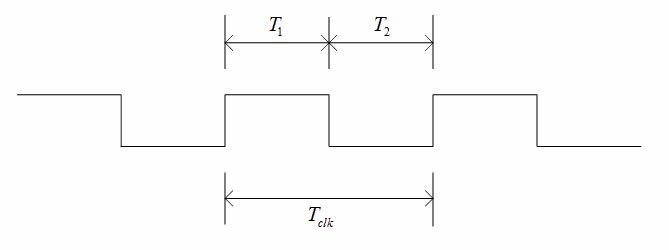

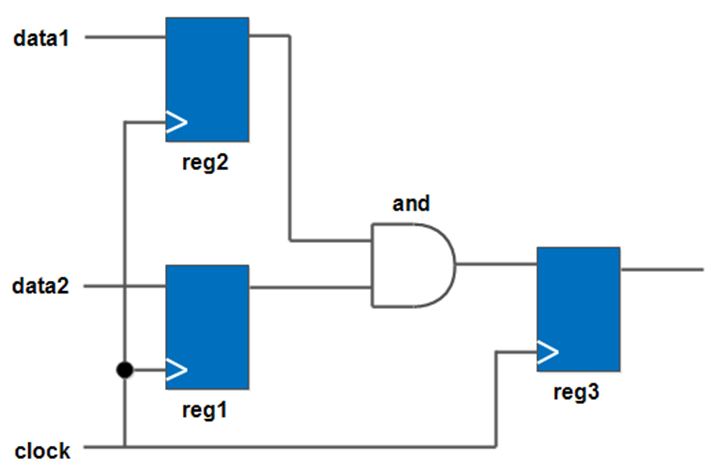

在这个波形中,我们看到clk_r3的前后各有一条虚线,前一条虚线到clk_r3上升沿的这段时间即建立时间,clk_r3上升沿到后一条虚线的这段时间即保持时间。前面对建立时间和保持时间下定义时提到过,在这段时间内不能够有数据的变化,数据必须保持稳定。而在这个波形中,也确实没有看到在建立时间和保持时间内,reg3in的数据有任何的变化,因此我们可以稳定的将reg3in的数据锁存到reg3的输出reg3out中。(特权同学,版权所有)

图8.10 建立时间和保持时间都满足要求的情况

如图8.11所示的波形,同样的一些信号,但我们发现reg3in在clk_r3的建立时间内发生了变化,这带来的后果就是clk_r3上升沿锁存到的reg3in数据不确定,那么随后的reg3out值也会处于一个不确定状态。比如第一个时钟周期,原本reg3in应该是稳定的低电平,但是由于整个路径上的延时时间过长,导致了reg3in在clk_r3的建立时间内数据还未能稳定下来,在建立时间内出现了电平正处于从高到低的变化,即不稳定的状态,那么导致的后果就是reg3out的最终输出不是确定的状态,很可能是忽高忽低的亚稳态,而不是原本期望的低电平。(特权同学,版权所有)

图8.11 建立时间违规的情况

我们再来看看保持时间违规的情况,如图8.12所示,这次是数据传输得太快了,原本应该下一个时钟周期到达clk_r3的数据竟然在clk_r3的前一个时钟周期的保持时间还未过去就来到了。因此,它出现的最终危害也是后端输出的reg3out处于不确定的状态。(特权同学,版权所有)

图8.12 保持时间违规的情况