FPGA实战演练逻辑篇63:CMOS摄像头接口时序设计3实际计算

0赞CMOS摄像头接口时序设计3实际计算(特权同学版权所有)

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

具体问题具体分析,我们当前的工程,状况和理想模型略有区别。实际上在上面这个模型的源寄存器端的很多信息都不用详细分析,因为我们获得的波形是来自于Sensor芯片的引脚上。同理,我们可以得到input delay的计算公式如下。(特权同学,版权所有)

Input max delay = (Tdpcb_max – Tcpcb_min) + Tco_max

Input min delay = (Tdpcb_min – Tcpcb_max) + Tco_min

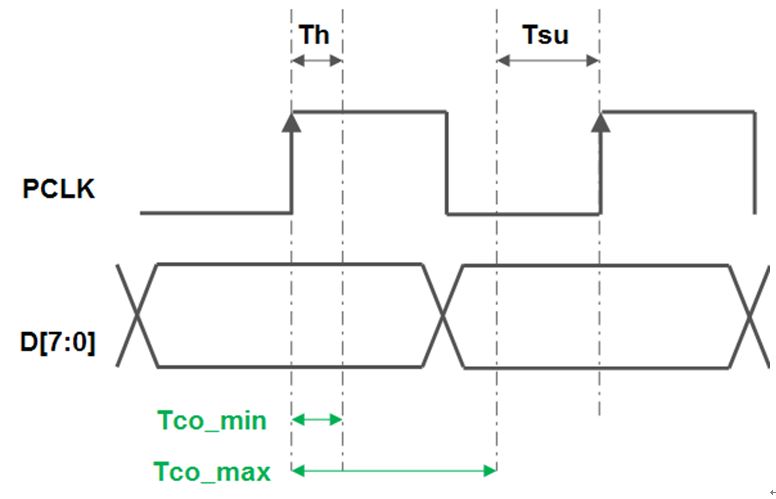

在这两个公式中,参数Tco是前面我们还未曾提到的,下面我们就要分析下如何得到这个参数。Tco指的是理想情况下数据在源寄存器被源时钟锁存后,经过多长时间输入到引脚上。前面我们已经得到了PCLK和D[7:0]之间的关系,其实从已知的关系中,我们不难推断出Tco_max和Tco_min,如图8.50所示。若PCLK的时钟周期为Tpclk,则:

Tco_max = Tpclk – Tsu

Tco_min = Th

在我们采样的CMOS Sensor图像中,PCLK频率为12.5MHz,即80ns。因此,我们可以计算到:

Tco_max = 80ns – 15ns = 65ns

Tco_min = 8ns

图8.50 Tco的最大和最小值示意

我们再看看PCB的走线情况,算算余下和PCB走线有关的延时。(特权同学,版权所有)

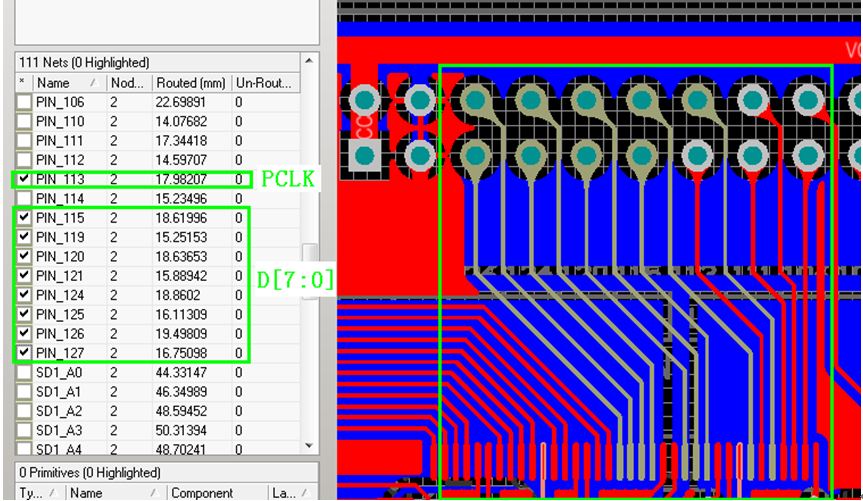

如图8.51所示,这是PCLK和D[7:0]在SF-CY3核心板上的走线。(特权同学,版权所有)

图8.51 PCLK和D[7:0]在SF-CY3板上的走线

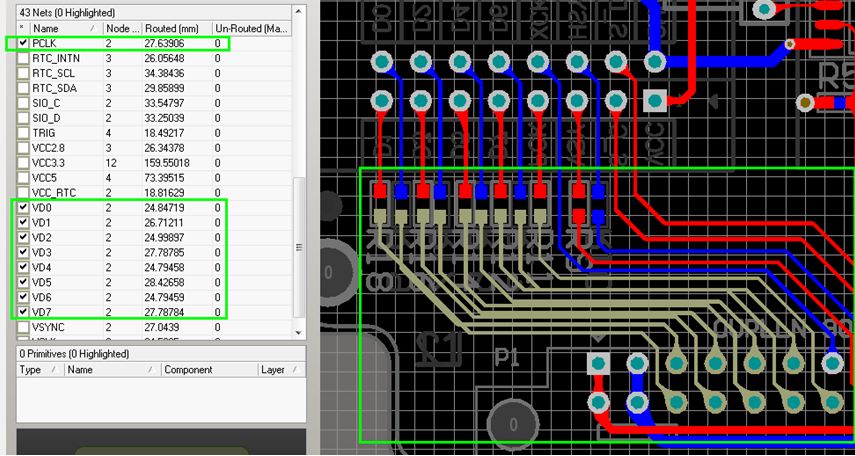

如图8.52和图8.53所示,这是PCLK和D[7:0]在SF-SENSOR子板上的走线,在这个板子上的走线由匹配电阻分为两个部分。(特权同学,版权所有)

图8.52 PCLK和D[7:0]在SF-SENSOR板上的走线1

图8.53 PCLK和D[7:0]在SF-SENSOR板上的走线2

根据前面的走线长度,我们可以换算一下相应的走线延时,如表8.3所示。因此,我们可以得到,Tcpcb_max = 0.35ns,Tcpcb_min = 0.35ns,Tdpcb_max = 0.36ns,Tdpcb_min = 0.31ns。(特权同学,版权所有)

表8.3 CMOS Sensor接口的走线延时换算表

信号名 | SF-CY3走线长度 | SF-SENSOR走线长度1 | SF-SENSOR走线长度2 | 总长度(mm) | 延时(ns) |

PCLK | 18 | 27.7 | 6 | 51.7 | 0.346023622 |

VD0 | 16.8 | 24.9 | 9.1 | 50.8 | 0.34 |

VD1 | 19.5 | 26.8 | 6 | 52.3 | 0.35003937 |

VD2 | 16.2 | 25 | 9.1 | 50.3 | 0.336653543 |

VD3 | 18.9 | 27.8 | 6 | 52.7 | 0.352716535 |

VD4 | 15.9 | 24.8 | 9.1 | 49.8 | 0.333307087 |

VD5 | 18.7 | 28.5 | 6 | 53.2 | 0.356062992 |

VD6 | 15.3 | 24.8 | 9.1 | 49.2 | 0.329291339 |

VD7 | 18.7 | 27.8 | 6 | 52.5 | 0.351377953 |

HREF | 14.6 | 23.8 | 9.1 | 47.5 | 0.317913386 |

将上面得到的具体数值都代入公式,得到:

Input max delay = (0.36ns – 0.35ns) + 65ns = 65.01ns

Input min delay = (0.31ns – 0.35ns) + 8ns = 7.96ns

加上一些余量,我们可以取input max delay = 66ns,input min delay = 7ns。(特权同学,版权所有)