EDN003 FPGA入门:内里本质探索——器件结构

0赞FPGA入门:内里本质探索——器件结构

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt

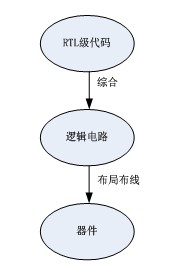

在第一章里,我们已经讨论了FPGA/CPLD的开发流程以及编译过程中产生的各种网表。在本章,我们也讨论了逻辑电路,那么它和代码以及最终的FPGA/CPLD器件之间又是怎样的关系?如图3.17所示,设计者先编写RTL级代码来描述自己需要实现的功能;然后在EDA工具中对其进行综合,RTL级的代码就被转换为逻辑电路,就如前面一节里的与、或、非等一大堆门电路的各种组合;最后这些逻辑电路需要被实现到特定的FPGA/CPLD器件中,我们称之为布局布线。

图3.17 代码、逻辑电路和器件

在谈到FPGA/CPLD的规模大小时,我们常常说FPGA/CPLD器件有多少门。因此,很多人就天真的以为FPGA/CPLD器件里面就是一大堆与门、或门、非门,设计者写好代码实现的逻辑就对应为FPGA/CPLD里面的各种不同门之间的相互连接。实际情况还真不是这么简单,FPGA/CPLD里面其实也找不着多少个与门、或门、非门。那么FPGA/CPLD器件内部到底以怎样的方式来实现我们需要的逻辑电路呢?下面我们就通过剖析MAX II家族CPLD器件的内部结构来解开这个迷。

翻开MAX II的器件手册,第2章是专门谈论器件结构(Architecture)的。为了帮助大家更好的理解这部分内容,除了对这个典型的CPLD器件结构进行介绍,我们还会列举一个实例来看看一段代码是如何被综合为逻辑电路,以及逻辑电路如何被映射到器件中。

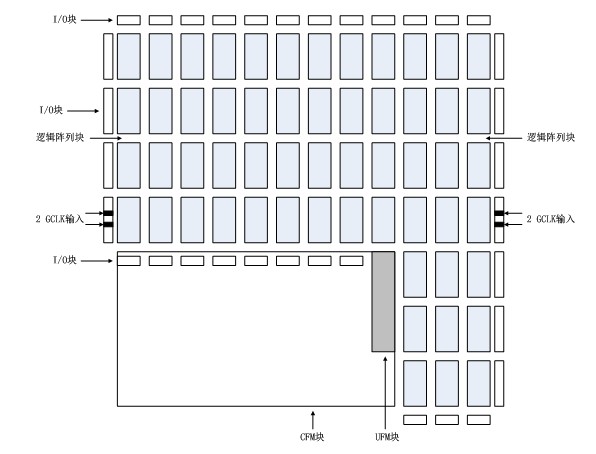

我们先看看MAX II这款器件的内部结构,如图3.18所示。器件当中最多的就是逻辑阵列块(Logic array blocks,简称LABs),每个LABs包含了10个逻辑单元(Logic elements,简称LEs),LEs是能够实现用户逻辑功能的最小单位,后面我们还会详细介绍这个LEs的内部结构。其实这个MAX II器件的逻辑结构在altera的器件中非常具有典型性,altera的FPGA也基本都是类似的内部结构。在器件的周围布满了I/O块,这些I/O块直接连接控制着器件外部裸露的I/O管脚。I/O块中包括了双向的I/O缓冲以及一些可编程的I/O特性功能,如施密特触发、上拉电阻和各种电平标准。I/O块的左右两侧各有2个GCLK管脚可用作全局时钟输入,这4个管脚输入的信号在器件内部具有低延时、高扇出等特性,不仅适合于时钟信号输入,也可以作为复位、置位等控制信号的输入。

图3.18 MAX II器件内部结构

在器件的左下角,有一个MAX II器件特有的CFM块(configuration flash memory)和UFM块(user flash memory),其实altera的这款CPLD器件和FPGA器件一样是基于SRAM的,只是其内部嵌入了一块用于存储配置数据流的flash存储器,即CFM块。有了CFM块,用户无需再像一般的FPGA一样专门给这款器件外挂一个用于存储配置数据流的非易失存储器了。UFM块则是供用户使用的flash存储区,关于这片存储区的应用在本书的实例部分会有详细的介绍。

虽然图3.18的结构图中没有示意出各个功能块之间的相互连接关系,但是大家可以想象,其实在各个功能块之间存在着丰富的可编程的互连线帮助实现最终的应用。比如各个行列LABs之间会有可编程的互连线、LABs内部的各个LEs内部之间也会有可编程的互连线、I/O块与LABs之间、LABs与UFM之间都有着灵活可编程的互连线。

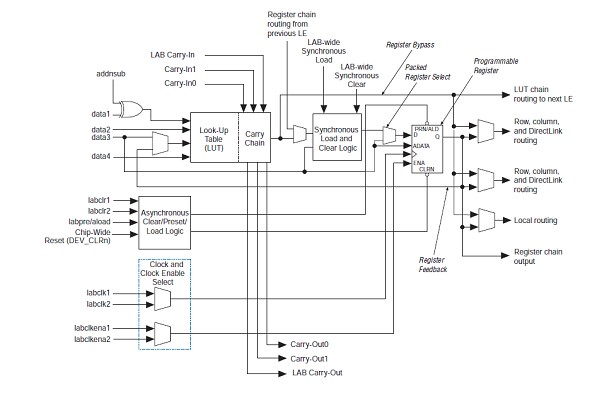

接下来我们再了解一下器件中最小的功能单元LEs的内部结构。如图3.19所示,这是在MAX II器件内部一个完整的LEs的内部结构。详细的各个模块以及功能介绍大家可以去研究MAX II的器件手册,简单的来看,有几样核心的东西是必须知道的。

图3.19 LEs内部结构

在图3.19右上的Programmable Register想必大家一定很眼熟,没有错,它正是我们在前文大书特书的寄存器,这可是实实在在存在着的,它的功能也大体和前面介绍的D触发器别无二致。再看左侧,有个4输入的查找表(Look-Up table,LUT),别小看它,功能可强大了,前面的各种逻辑门需要实现的输入输出关系大多时候是通过这个LUT来实现的。此外,还有一些诸如进位链(Carry chain)是用来协助实现运算功能的,各种布线(routing)连接则是用于实现该LEs与外部互连功能。总之,这个结构几乎可以满足大多数的逻辑电路需求,当然了,并非这么个结构框架里的所有东西在每个电路实现中都能派上用场。正所谓“可编程”(Programmable),设计者所需要实现的电路会根据具体的情况来开启或关闭各个模块的使用或连接。

通常MAX II器件的LEs结构在实际应用中为了达到功能的最优化,会被作为正常模式(Normal Mode)或动态算术模式(Dynamic Arithmetic Mode)使用。两种模式对LEs资源的使用有所不同,总之大家记住一个点,加减等运算用算术模式实现是最佳的选择,其他情况下一般是正常模式来实现,而到底用哪种模式来实现也不用设计者操心,Quartus II软件会自动判断和优化,咱只要知道有这么一回事就好。我们看图3.20,这是正常模式下的LEs结构,相比于完整的LEs结构,少了好多功能块。

图3.20 正常模式下的LEs

说了这么多理论,估计大伙都有些头大了。下面举个例子,让大家看看一个简单的逻辑功能是如何用这个正常模式下的LEs来实现的。有如下一段Verilog代码:

module p22vlg(

clk,rst_n,

ain,bin,cin,dout

);

input clk;

input rst_n;

input ain,bin,cin;

output reg dout;

always @(posedge clk or negedge rst_n)

if(!rst_n) dout <= 1'b0;

else dout <= (ain & bin) | cin;

endmodule

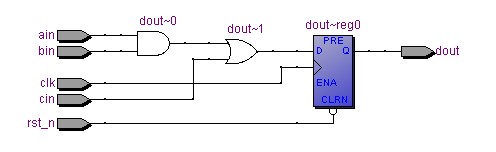

看不懂不要紧,咱还没开始学语法呢。这个电路中,输入信号ain、bin和cin,复位信号rst_n,时钟信号clk,输出信号dout。输出信号dout在复位信号rst_n有效时输出为0,在撤销复位(rst_n = 1)后每个时钟上升沿锁存当前的最新值,这个最新值为当前输入信号ain与bin再或cin的结果。其逻辑功能如图3.21所示,是一个典型的时序逻辑,这个电路中有我们前面提到的与门、或门和寄存器等基本组件。

图3.21 逻辑功能视图

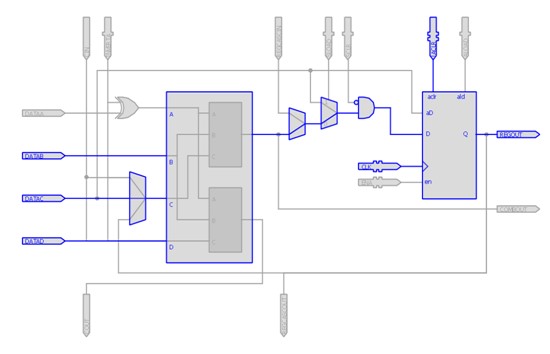

再看经过Quartus II工具的“翻译”后,前面这段逻辑被映射到了MAX II的LEs中,和图3.20相比较,可以确认这是LEs的正常模式,图中高亮部分是被“编程”开启功能的电路实现。不要感到稀奇,这个原本要实现与门、或门等逻辑功能的电路却不是用与门、或门来实现的,而是我们前面提到的LUT在这里扮演了很重要的角色。有人可能又要纳闷了LUT到底为何物?有那么神通广大么?别说,还真那么回事。就拿4输入的LUT来说,其实它里面就相当于一个16bit的存储器,或者你也可以理解LUT里面存放着4个输入信号的真值表,输入信号通过这个真值表便可得到期望的结果,就如我们这个实例一样。

图3.22 LEs中的逻辑实现

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt