例说FPGA连载85:工业现场实时监控界面设计之AD采集模块代码解析

1赞

发表于 3/30/2017 3:11:36 PM

阅读(3824)

例说FPGA连载85:工业现场实时监控界面设计之AD采集模块代码解析

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

该模块中,主要实现实时的AD采样控制功能,通过SPI接口定时的采集AD芯片TLC549转换输出的电压值。这些电压值通过8bit总线接口sys_rddata输出,在顶层模块sys_rddata总线将连接到NIOS II的8bit输入PIO上,随时供读取。

该模块的内部功能框图如图17.11所示。分频计数逻辑产生SPI控制的基准时钟节拍,状态机定时的进入数据采集状态,产生必要的SPI时序,读取SPI数据线上的8bit值,延时计数器逻辑产生每两次采集间大于17us的最小延时(TLC549芯片要求)。

图17.11 ADC控制器模块功能框图

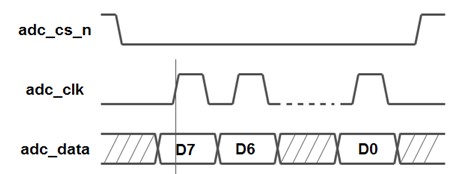

AD芯片TLC549的控制使用了比较简化(单向数据传输)的SPI接口,接口上只需要片选信号adc_cs_n、时钟信号adc_clk和输入数据信号adc_data。控制时序如图17.12所示,在片选信号有效后稍作延时,随后产生8个时钟周期依次读取AD采样的8bit数据即可。在片选信号拉低后大约1.4us,第一个采样数据出现在数据信号adc_data上,对应时钟信号adc_clk的上升沿可以采样数据,时钟信号adc_clk的最高频率可以达到1.1MHz。两次数据采样间隔必须大于17us。其它相关时序参数可以参考TLC549的datasheet,。

图17.12 ADC芯片写数据时序波形