勇敢的芯伴你玩转Altera FPGA连载43:基于仿真的第一个工程实例之Verilog语法检查

0赞

发表于 1/22/2018 9:16:26 PM

阅读(3466)

勇敢的芯伴你玩转Altera FPGA连载43:基于仿真的第一个工程实例之Verilog语法检查

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1i5LMUUD

为了验证一下设计输入的代码的基本语法是否正确,可以点击“Flow à Compilation”下的“Analysis & Elaboration”按钮,如图6.8所示。

图6.8 编译源码

语法检查完成后,如图6.9所示。“Analysis & Elaboration”按钮前面打上了绿色的勾。

图6.9 语法检查成功

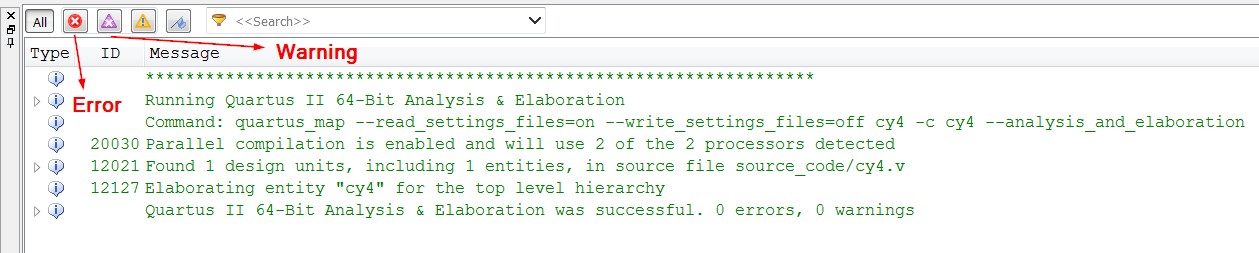

同时我们可以查看打印窗口的Processing里的信息,包括各种warning和Error。Error是不得不关注的,因为Error意味着我们的代码有语法错误,后续的编译将无法继续;而warning则不一定是致命的,但很多时候warning中暗藏玄机,很多潜在的问题都可以从这些条目中寻找到蛛丝马迹。当然了,也并不是说一个设计编译下来就不可以有warning,如果设计者确认这些warning符合我们的设计要求,那么可以忽略它。

图6.10 语法检查打印信息